[静态时序分析简明教程(一)] 绪论

静态时序分析简明教程一:绪论

- 一、写在前面

- 1.1 快速导航链接·

- 二、什么是静态时序分析

- 三、为什么需要时序约束

- 四、约束的第一步:综合

- 4.1 什么是综合

- 4.2 综合与时序约束的关系

- 4.2.1 输入重排序

- 4.2.2 输入的缓冲

- 五、总结

一、写在前面

一个数字芯片工程师的核心竞争力是什么?不同的工程师可能给出不同的答复,有些人可能提到硬件描述语言,有些人可能会提到对于特定算法和协议的理解,有些人或许会提到对于软硬件的结合划分,作者想说,这些说法,其实对也不对,硬件描述语言,翻来覆去无非是always和assign这几个语句的反复使用,而一些基础的协议算法,深究起来其实也并不复杂,于作者而言,在常规的技能以外,有两项额外的技能颇为重要,其中之一便为sdc/STA的分析能力,它的重要之处在于作为桥梁建立了前端和后端的连接,虽然对于DE工程师而言,初版交付的sdc往往不甚准确,也没有办法通过这份sdc生成一份无误的timing report,但sdc的内容体现却是完完整整的将时序约束从行为级的描述映射到了gate level这样一个真实的电路层次上面。

写此专栏,一为学习记录,二为交流分享,以犒粉丝读者。

1.1 快速导航链接·

静态时序分析简明教程(一)绪论

静态时序分析简明教程(二)基础知识:建立保持时间,时序分析路径

静态时序分析简明教程(三)备战秋招,如何看懂一个陌生的timing report

静态时序分析简明教程(四)时钟常规约束

静态时序分析简明教程(五)时钟其他特性

静态时序分析简明教程(六)端口延迟

静态时序分析简明教程(七)完整端口约束

静态时序分析简明教程(八)虚假路径

静态时序分析简明教程(九)多周期路径

静态时序分析简明教程(十)组合电路路径

静态时序分析简明教程(十一)模式分析与约束管理

静态时序分析简明教程(十二)浅议tcl语言

二、什么是静态时序分析

众所周知,PPA这三个要素的合理平衡,是一款芯片能否成功的重要因素,Power Performance Area中,performance的衡量可以有很多因素,其中就包括频率性能,也就是时序需求,STA静态时序分析就是检查所设计的电路是否能满足时序需求的方法,设计工程师会在综合之后根据设计的sdc进行一次初步的STA检查,但是在综合阶段,许多关于时钟网络的假设其实是不可用的,只有当完成布局规划,做完时钟树综合,才能得到一个相对准确的时序分析结果,因此DE工程师是第一遍尝试STA分析的芯片设计人员。

三、为什么需要时序约束

常规的芯片设计团队往往很少考虑时序问题,因为对于他们而言,他们的目标更多的聚焦于如何实现功能需求,物理设计团队负责满足时序要求,但是他们不清楚设计的内部结构,因此他们需要依靠于DE来实现时序约束。约束领域充满了细微的差别:不同的约束方式,虽然可能对于逻辑功能来说区别不大,但是会实打实的影响硬件设计的性能,进而影响芯片的质量,因此正确的理解和书写约束,变得非常重要。

四、约束的第一步:综合

时序约束最终是作用在真实电路上的延时约束,从Verilog这样一个行为级的描述过渡到真实的电路所需要经历的步骤被叫做综合,因此在绪论中,我们也需要搞明白综合是什么和综合是怎么作用在时序约束上的这两大问题。

4.1 什么是综合

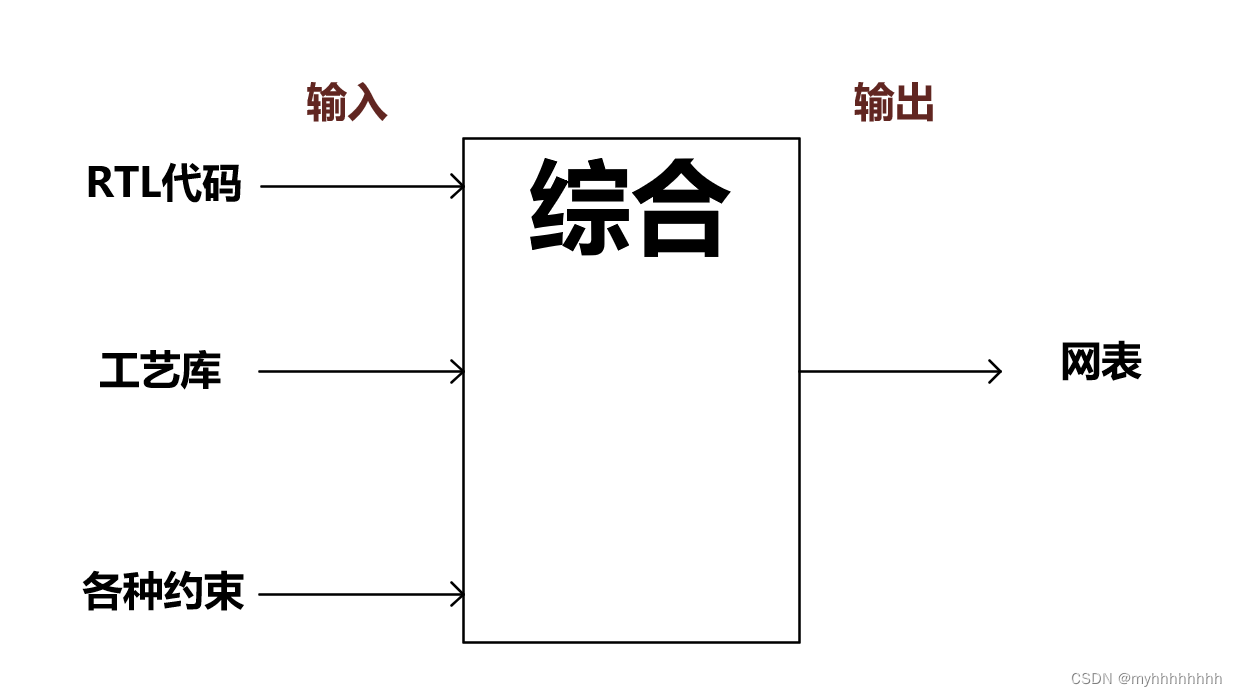

综合就是,在约束条件(时序约束、面积约束)下,使用特定厂商的工艺库(TSMC 7nm/5nm),将RTL代码(Verilog),转变为网表(记录wire/DFF等门级电路信息)的一个步骤,一个形象的图片如下:

4.2 综合与时序约束的关系

综合过程中面积优先/时序优先/时序的约束等不同的综合策略切实的影响着静态时序分析的结果,具体的原因可以简明分析两种如下

4.2.1 输入重排序

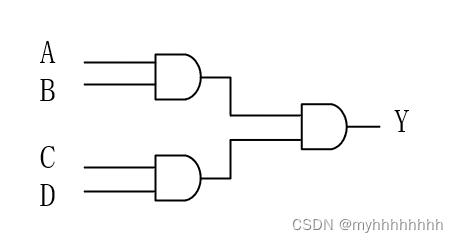

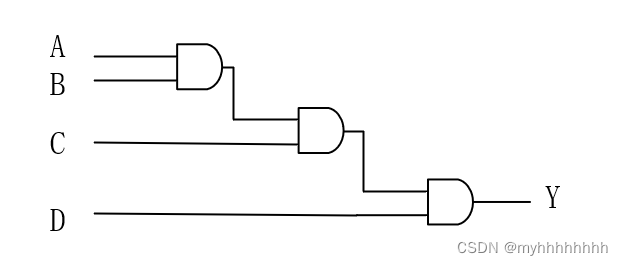

以下的例子切实的反映了综合结果对于时序的影响,两种逻辑排布在逻辑的层面上是一样的,有着相同的真值表,但是对于第一张图片而言,输入经过两级逻辑就可以抵达输出Y,而对于下面的图片而言,输入需要经过三级逻辑才可以抵达输出Y,具体选择哪种逻辑是根据时序约束决定的,通常情况下,大家会认为第一种会比第二种排列好,因为delay少。

但这个说法实际不绝对,因为delay的长短可以分别使建立时间和保持时间的压力变小,不过修保持时间的方法简单,修建立时间的方法复杂困难,因此更倾向于使用第一种逻辑排布,优先保证建立时间而已。

4.2.2 输入的缓冲

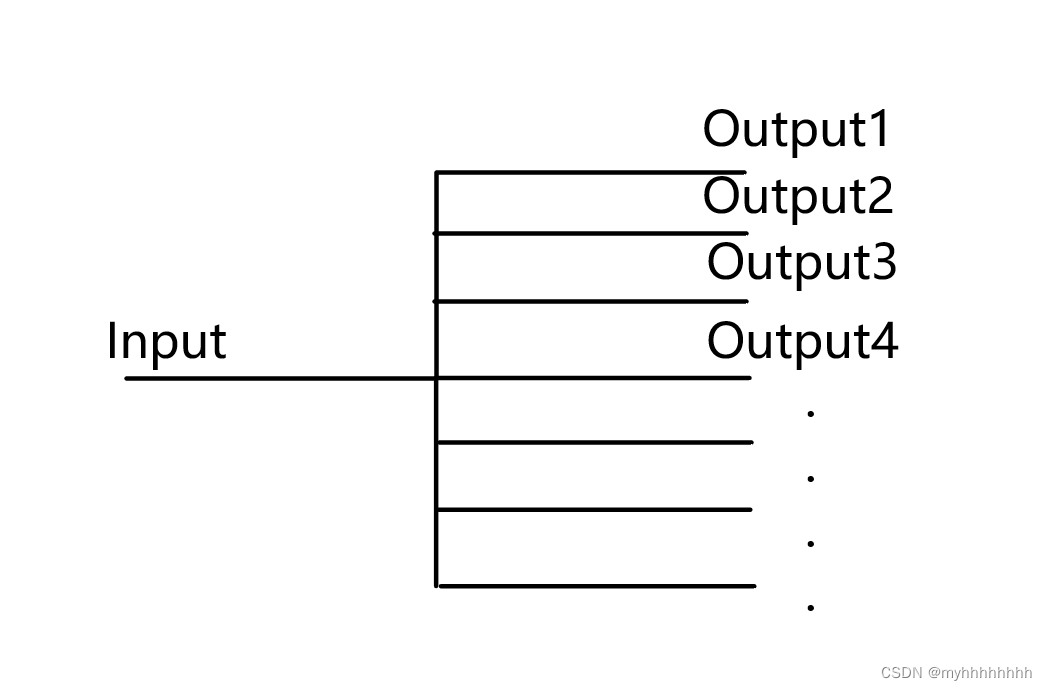

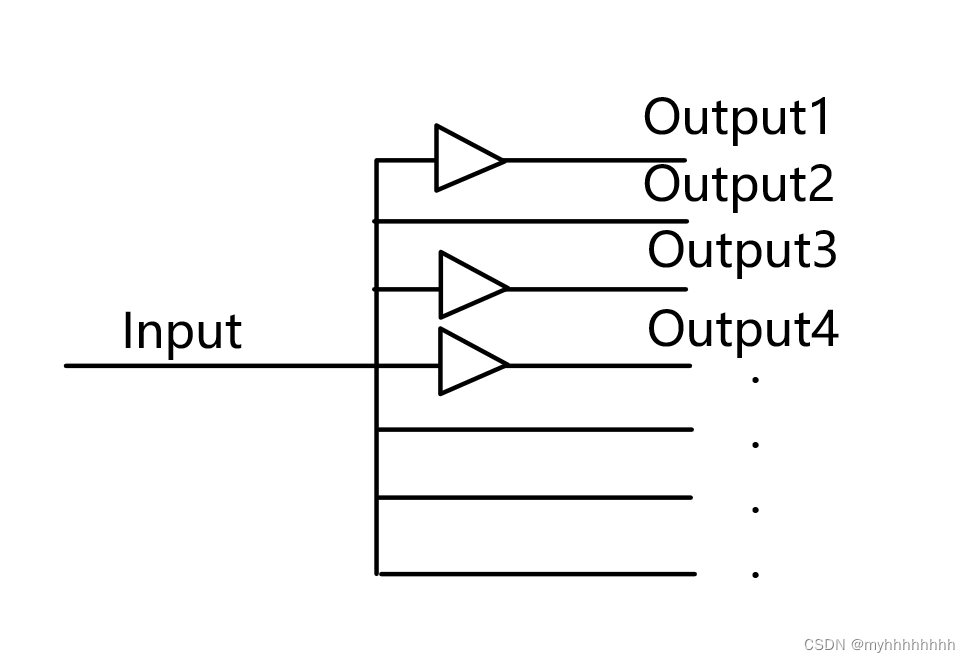

除了上面的例子,我们可以再举一个例子说明综合对于静态时序分析的影响,同样的一个输出不做改变的赋值给八个新的端口,以下的两种综合结果对应的HDL语言是一致的

但是综合出来的电路中,第二种逻辑排布的output1,output3和output4分别插入了buffer,增强了驱动,因此他们这几个端口的后续门电路的开启和关闭会比output2快(电子在端口的积累速度快),在这种层面上影响了静态时序分析的结果。

五、总结

在本文中,我们讨论了什么是时序分析和它的意义,接着介绍了时序约束的第一步:综合,重点从不同综合结果对于时序影响的层面上展开分析。