RISC_CPU模块的调试

代码:

cpu.v

`include "clk_gen.v"

`include "accum.v"

`include "adr.v"

`include "alu.v"

`include "machine.v"

`include "counter.v"

`include "machinectl.v"

`include "register.v"

`include "datactl.v"module cpu(clk,reset,halt,rd,wr,addr,data);input clk,reset;output rd,wr,addr,halt;inout data;wire clk,reset,halt;wire [7:0] data;wire [12:0] addr;wire rd,wr;wire clk1,fetch,alu_clk;wire [2:0] opcode;wire [12:0] ir_addr,pc_addr;wire [7:0] alu_out,accum;wire zero,inc_pc,load_acc,load_pc,load_ir,data_ena,contr_ena;clk_gen m_clk_gen (.clk(clk),.clk1(clk1),.fetch(fetch),.alu_clk(alu_clk),.reset(reset));register m_register (.data(data),.ena(load_ir),.rst(reset),.clk1(clk1),.opc_iraddr({opcode,ir_addr}));accum m_accum (.data(alu_out),.ena(load_acc),.clk1(clk1),.rst(reset),.accum(accum));alu m_alu (.data(data),.accum(accum),.alu_clk(alu_clk),.opcode(opcode),.alu_out(alu_out),.zero(zero));machinectl m_machinecl(.ena(contr_ena),.fetch(fetch),.rst(reset));machine m_machine (.inc_pc(inc_pc),.load_acc(load_acc),.load_pc(load_pc),.rd(rd), .wr(wr), .load_ir(load_ir), .clk1(clk1),.datactl_ena(data_ena), .halt(halt), .zero(zero),.ena(contr_ena),.opcode(opcode));datactl m_datactl (.in(alu_out),.data_ena(data_ena),.data(data));adr m_adr (.fetch(fetch),.ir_addr(ir_addr),.pc_addr(pc_addr),.addr(addr));counter m_counter (.ir_addr(ir_addr),.load(load_pc),.clock(inc_pc),.rst(reset),.pc_addr(pc_addr));endmodule

//--------------------------------------- cpu.v ????? -------------------------------------------------

ram.v

// --------------- RAM?ROM ----------------------------------------

module ram( data, addr, ena, read, write );

inout [7:0] data;

input [9:0] addr;

input ena;

input read, write;

reg [7:0] ram [10'h3ff:0];assign data = ( read && ena )? ram[addr] : 8'hzz;always @(posedge write)

begin

ram[addr]<=data;

end

endmodulerom.v

module rom( data, addr, read, ena );

output [7:0] data;

input [12:0] addr;

input read, ena;

reg [7:0] memory [13'h1fff:0];

wire [7:0] data;assign data= ( read && ena )? memory[addr] : 8'bzzzzzzzz;endmoduleaddr_decode.v

//--------------?????----------------------

module addr_decode( addr, rom_sel, ram_sel);

output rom_sel, ram_sel;

input [12:0] addr;

reg rom_sel, ram_sel;always @( addr )

begin

casex(addr)

13'b1_1xxx_xxxx_xxxx:{rom_sel,ram_sel}<=2'b01;

13'b0_xxxx_xxxx_xxxx:{rom_sel,ram_sel}<=2'b10;

13'b1_0xxx_xxxx_xxxx:{rom_sel,ram_sel}<=2'b10;

default:{rom_sel,ram_sel}<=2'b00;

endcase

end

endmodule/* ????????????????ROM?RAM?

FFFFH---1800H RAM

1800H---0000H ROM -----------------------------*/cputop.v

//------------------------------------------- cputop.v ????? -----------------------------------------------------

/***********************************************************************

*** ?????cputop ????????????????cpu???????????

*** ???????????????????????????????

*** ??????????????????????CPU????RTL??

*** ??????????????

************************************************************************/

`include "ram.v"

`include "rom.v"

`include "addr_decode.v"

`include "cpu.v"`timescale 1ns / 100ps

`define PERIOD 100 // matches clk_gen.v

module cputop;reg reset_req,clock;integer test;reg [(3*8):0] mnemonic; //array that holds 3 8-bit ASCII charactersreg [12:0] PC_addr,IR_addr;wire [7:0] data;wire [12:0] addr;wire rd,wr,halt,ram_sel,rom_sel;//------------------------ cpu ?????????ROM?RAM?????--------------------------------------

cpu t_cpu (.clk(clock),.reset(reset_req),.halt(halt),.rd(rd),.wr(wr),.addr(addr),.data(data));ram t_ram (.addr(addr[9:0]),.read(rd),.write(wr),.ena(ram_sel),.data(data));rom t_rom (.addr(addr),.read(rd),.ena(rom_sel),.data(data));addr_decode t_addr_decode (.addr(addr),.ram_sel(ram_sel),.rom_sel(rom_sel));//--------------------cpu ?????????ROM?RAM???????----------------------------------

initialbegin clock=1;//display time in nanoseconds$timeformat ( -9, 1, " ns", 12);display_debug_message;sys_reset;test1;$stop;test2;$stop;test3;$stop;

endtask display_debug_message;begin$display("\n**************************************************");$display("* THE FOLLOWING DEBUG TASK ARE AVAILABLE: *");$display("* \"test1; \" to load the 1st diagnostic progran. *");$display("* \"test2; \" to load the 2nd diagnostic program. *");$display("* \"test3; \" to load the Fibonacci program. *");$display("*****************************************************\n");endendtasktask test1;begintest = 0;disable MONITOR;$readmemb ("test1.pro", t_rom.memory);$display("rom loaded successfully!");$readmemb("test1.dat",t_ram.ram);$display("ram loaded successfully!");#1 test = 1;#14800 ;sys_reset;endendtasktask test2;begintest = 0;disable MONITOR;$readmemb("test2.pro",t_rom.memory);$display("rom loaded successfully!");$readmemb("test2.dat",t_ram.ram);$display("ram loaded successfully!");#1 test = 2;#11600;sys_reset;endendtasktask test3;begintest = 0;disable MONITOR;$readmemb("test3.pro",t_rom.memory);$display("rom loaded successfully!");$readmemb("test3.dat",t_ram.ram);$display("ram loaded successfully!");#1 test = 3;#94000;sys_reset;endendtasktask sys_reset;beginreset_req = 0;#(`PERIOD*0.7) reset_req = 1; #(1.5*`PERIOD) reset_req = 0; endendtask always @(test)begin: MONITORcase (test)1: begin //display results when running test 1$display("\n*** RUNNING CPUtest1 - The Basic CPU Diagnostic Program ***");$display("\n TIME PC INSTR ADDR DATA ");$display(" ---------- ---- ----- ----- ----- ");while (test == 1) @(t_cpu.m_adr.pc_addr)//fixedif ((t_cpu.m_adr.pc_addr%2 == 1)&&(t_cpu.m_adr.fetch == 1))//fixed begin# 60 PC_addr <=t_cpu.m_adr.pc_addr -1 ;IR_addr <=t_cpu.m_adr.ir_addr;# 340 $strobe("%t %h %s %h %h", $time, PC_addr, mnemonic, IR_addr,data );//HERE DATA HAS BEEN CHANGED T-CPU-M-REGISTER.DATAend end2: begin$display("\n*** RUNNING CPUtest2 - The Advanced CPU Diagnostic Program ***");$display("\n TIME PC INSTR ADDR DATA ");$display(" ---------- --- ----- ----- ---- ");while (test == 2) @(t_cpu.m_adr.pc_addr)if ((t_cpu.m_adr.pc_addr%2 == 1) && (t_cpu.m_adr.fetch == 1))begin # 60 PC_addr <= t_cpu.m_adr.pc_addr - 1 ;IR_addr <= t_cpu.m_adr.ir_addr;# 340 $strobe("%t %h %s %h %h", $time, PC_addr,mnemonic, IR_addr, data );end end3: begin$display("\n*** RUNNING CPUtest3 - An Executable Program ***"); $display("*** This program should calculate the fibonacci ***");$display("\n TIME FIBONACCI NUMBER");$display( " --------- -----------------");while (test == 3)begin wait ( t_cpu.m_alu.opcode == 3'h1) // display Fib. No. at end of program loop$strobe("%t %d", $time,t_ram.ram[10'h2]);wait ( t_cpu.m_alu.opcode != 3'h1);endend endcaseend

//-------------------------------------------------------------------------

always @(posedge halt) //STOP when HALT instruction decodedbegin#500 $display("\n*********************************************");$display( "** A HALT INSTRUCTION WAS PROCESSED !!! **");$display( "*********************************************\n");end

always #(`PERIOD/2) clock=~clock;

always @(t_cpu.m_alu.opcode) //get an ASCII mnemonic for each opcodecase(t_cpu.m_alu.opcode)3'b000 : mnemonic ="HLT";3'h1 : mnemonic = "SKZ";3'h2 : mnemonic = "ADD";3'h3 : mnemonic = "AND";3'h4 : mnemonic = "XOR";3'h5 : mnemonic = "LDA";3'h6 : mnemonic = "STO";3'h7 : mnemonic = "JMP";default : mnemonic = "???";endcaseendmodule

//------------------------------------------- cputop.v ????? -----------------------------------------------------

仿真:

sim:/cputop/rom_sel

run -all

#

# **************************************************

# * THE FOLLOWING DEBUG TASK ARE AVAILABLE: *

# * "test1; " to load the 1st diagnostic progran. *

# * "test2; " to load the 2nd diagnostic program. *

# * "test3; " to load the Fibonacci program. *

# *****************************************************

#

# rom loaded successfully!

# ram loaded successfully!

#

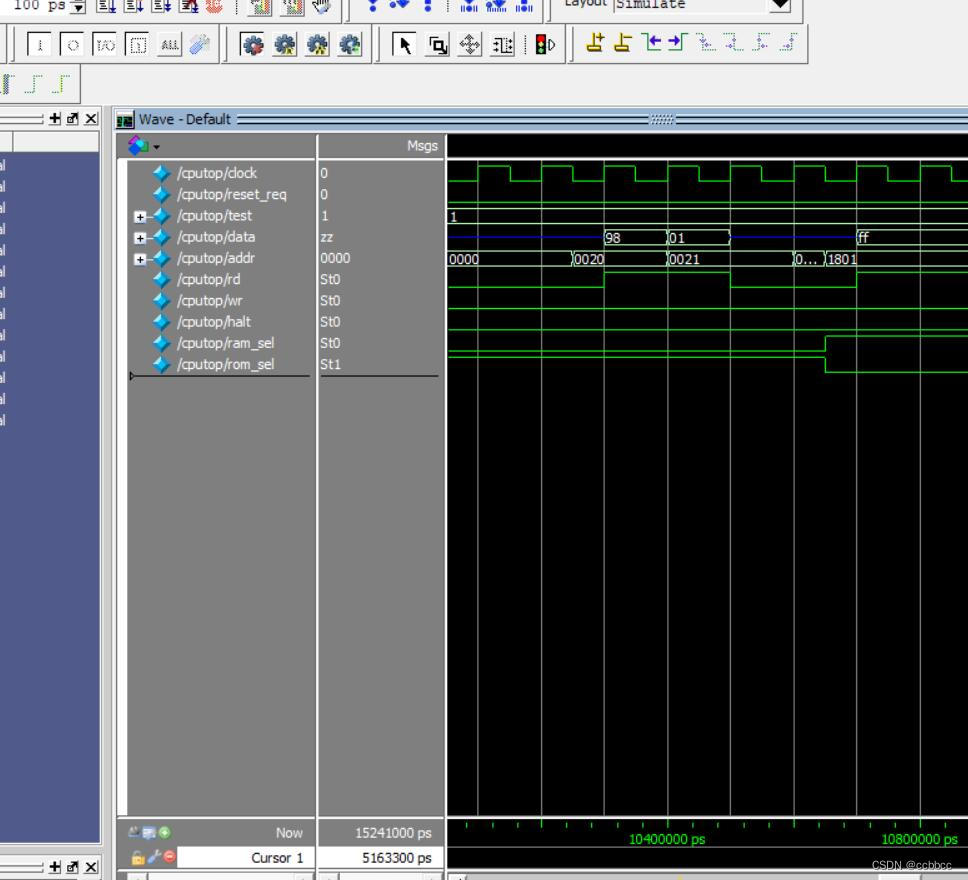

# *** RUNNING CPUtest1 - The Basic CPU Diagnostic Program ***

#

# TIME PC INSTR ADDR DATA

# ---------- ---- ----- ----- -----

# 1200.0 ns 0000 JMP 003c zz

# 2000.0 ns 003c JMP 0006 zz

# 2800.0 ns 0006 LDA 1800 00

# 3600.0 ns 0008 SKZ 0000 zz

# 4400.0 ns 000c LDA 1801 ff

# 5200.0 ns 000e SKZ 0000 zz

# 6000.0 ns 0010 JMP 0014 zz

# 6800.0 ns 0014 STO 1802 ff

# 7600.0 ns 0016 LDA 1800 00

# 8400.0 ns 0018 STO 1802 00

# 9200.0 ns 001a LDA 1802 00

# 10000.0 ns 001c SKZ 0000 zz

# 10800.0 ns 0020 XOR 1801 ff

# 11600.0 ns 0022 SKZ 0000 zz

# 12400.0 ns 0024 JMP 0028 zz

# 13200.0 ns 0028 XOR 1801 ff

# 14000.0 ns 002a SKZ 0000 zz

# 14800.0 ns 002e HLT 0000 zz

#

# *********************************************

# ** A HALT INSTRUCTION WAS PROCESSED !!! **

# *********************************************

#

# Break in Module cputop at E:/FPGA/study/cpu/cputop.v line 43

quit -sim

# rom loaded successfully!

# ram loaded successfully!

#

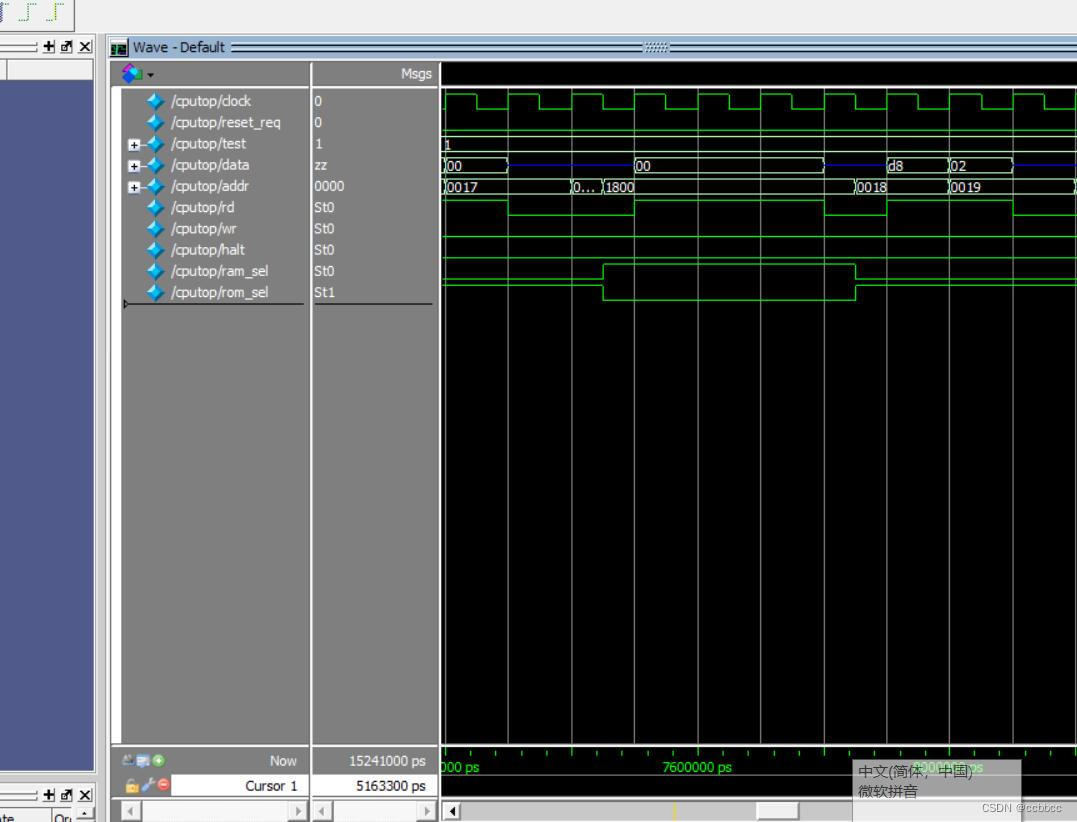

# *** RUNNING CPUtest2 - The Advanced CPU Diagnostic Program ***

#

# TIME PC INSTR ADDR DATA

# ---------- --- ----- ----- ----

# 16200.0 ns 0000 LDA 1801 aa

# 17000.0 ns 0002 AND 1802 ff

# 17800.0 ns 0004 XOR 1801 aa

# 18600.0 ns 0006 SKZ 0000 zz

# 19400.0 ns 000a ADD 1800 01

# 20200.0 ns 000c SKZ 0000 zz

# 21000.0 ns 000e JMP 0012 zz

# 21800.0 ns 0012 XOR 1802 ff

# 22600.0 ns 0014 ADD 1800 01

# 23400.0 ns 0016 STO 1803 ff

# 24200.0 ns 0018 LDA 1800 01

# 25000.0 ns 001a ADD 1803 ff

# 25800.0 ns 001c SKZ 0000 zz

# 26600.0 ns 0020 HLT 0000 zz

#

# *********************************************

# ** A HALT INSTRUCTION WAS PROCESSED !!! **

# *********************************************

#

# Break in Module cputop at E:/FPGA/study/cpu/cputop.v line 45

run -continue

# rom loaded successfully!

# ram loaded successfully!

#

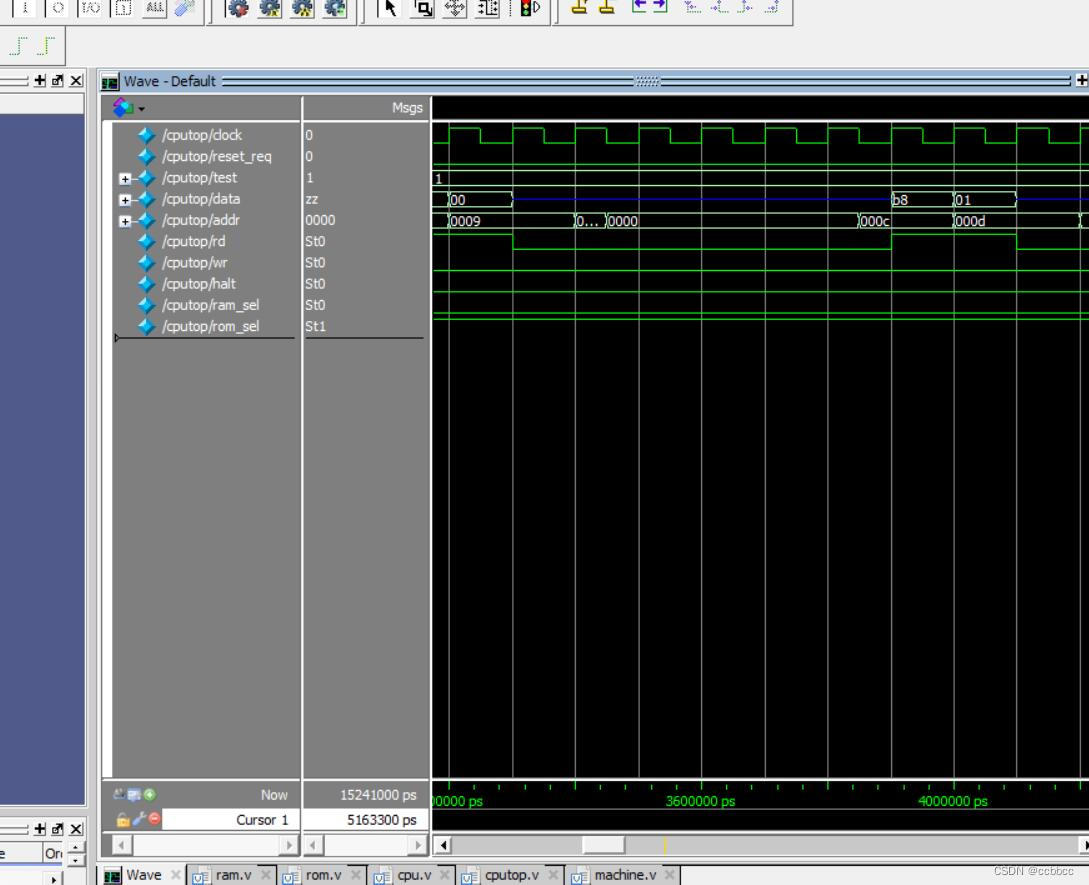

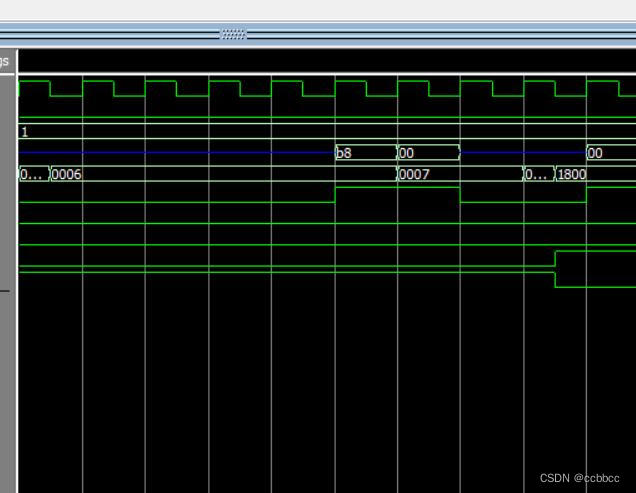

# *** RUNNING CPUtest3 - An Executable Program ***

# *** This program should calculate the fibonacci ***

#

# TIME FIBONACCI NUMBER

# --------- -----------------

# 33250.0 ns 0

# 40450.0 ns 1

# 47650.0 ns 1

# 54850.0 ns 2

# 62050.0 ns 3

# 69250.0 ns 5

# 76450.0 ns 8

# 83650.0 ns 13

# 90850.0 ns 21

# 98050.0 ns 34

# 105250.0 ns 55

# 112450.0 ns 89

# 119650.0 ns 144

#

# *********************************************

# ** A HALT INSTRUCTION WAS PROCESSED !!! **

# *********************************************

#

# Break in Module cputop at E:/FPGA/study/cpu/cputop.v line 47

# Break key hit