Verilog if语句阻断z状态传播

一、测试代码

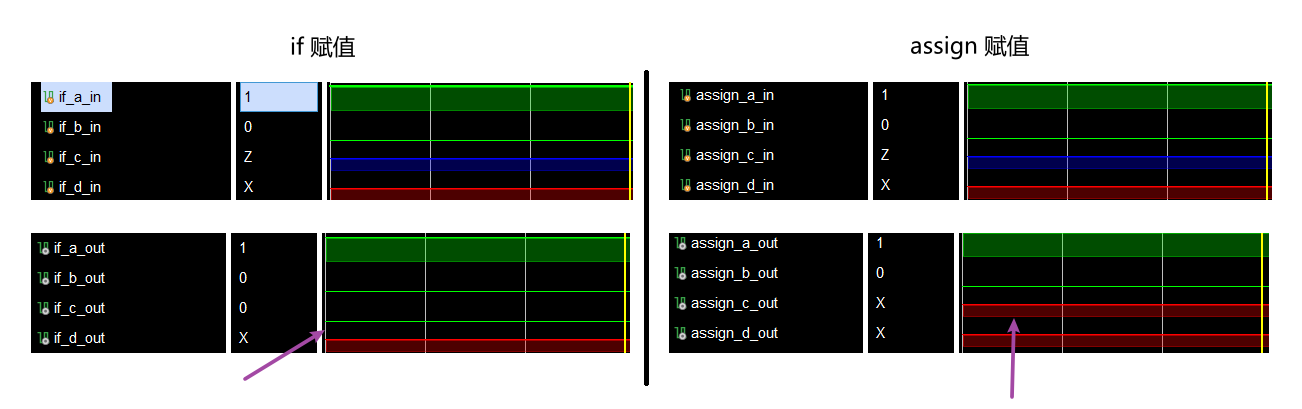

设置两组输入输出,对比使用assign赋值语句与always if语句。

- if_assign_test.v

`timescale 1ns / 1ps

//

// Engineer: wkk

// Module Name: if_assign_test

//

module if_assign_test(input if_a_in,input if_b_in,input if_c_in,input if_d_in,input assign_a_in,input assign_b_in,input assign_c_in,input assign_d_in,output reg if_a_out,output reg if_b_out,output reg if_c_out,output reg if_d_out,output assign_a_out,output assign_b_out,output assign_c_out,output assign_d_out

);assign assign_a_out = assign_a_in ? 1'b1:1'b0;

assign assign_b_out = assign_b_in ? 1'b1:1'b0;

assign assign_c_out = assign_c_in ? 1'b1:1'b0;

assign assign_d_out = assign_d_in ? 1'b1:1'b0;always @( * ) beginif( if_a_in ) beginif_a_out = 1'b1;end else beginif_a_out = 1'b0;end

endalways @( * ) beginif( if_b_in ) beginif_b_out = 1'b1;end else beginif_b_out = 1'b0;end

endalways @( * ) beginif( if_c_in ) beginif_c_out = 1'b1;end else beginif_c_out = 1'b0;end

endalways @( * ) beginif( if_d_in ) beginif_d_out = 1'b1;end else beginif_d_out = 1'b0;end

endendmodule

- tb_if_assign_test.v

`timescale 1ns / 1ps

//

// Engineer: wkk

// Create Date: 2023/12/05 20:37:07

// Module Name: tb_if_assign_test

//module tb_if_assign_test();

reg if_a_in;

reg if_b_in;

reg if_c_in;

reg if_d_in;

reg assign_a_in;

reg assign_b_in;

reg assign_c_in;

reg assign_d_in;wire if_a_out;

wire if_b_out;

wire if_c_out;

wire if_d_out;wire assign_a_out;

wire assign_b_out;

wire assign_c_out;

wire assign_d_out;if_assign_test if_assign_test_inst (.if_a_in (if_a_in),.if_b_in (if_b_in),.if_c_in (if_c_in),.if_d_in (if_d_in),.assign_a_in(assign_a_in),.assign_b_in(assign_b_in),.assign_c_in(assign_c_in),.assign_d_in(assign_d_in),.if_a_out (if_a_out),.if_b_out (if_b_out),.if_c_out (if_c_out),.if_d_out (if_d_out),.assign_a_out(assign_a_out),.assign_b_out(assign_b_out),.assign_c_out(assign_c_out),.assign_d_out(assign_d_out)

);initial beginif_a_in = 1'b1;if_b_in = 1'b0;if_c_in = 1'bz;if_d_in = 1'bx;assign_a_in = 1'b1;assign_b_in = 1'b0;assign_c_in = 1'bz;assign_d_in = 1'bx;# 100;$finish;

end

endmodule

二、仿真结果

通过if ( 条件 ) 的方式,z态被阻断了。