Quartus 软件界面介绍与部分使用技巧

内容太多,只能慢慢补充完善了~

对一个软件的熟练掌握,不仅在于完成项目工程,还在于对一个软件的各个功能的位置与使用要熟稔于心(个人看法)。

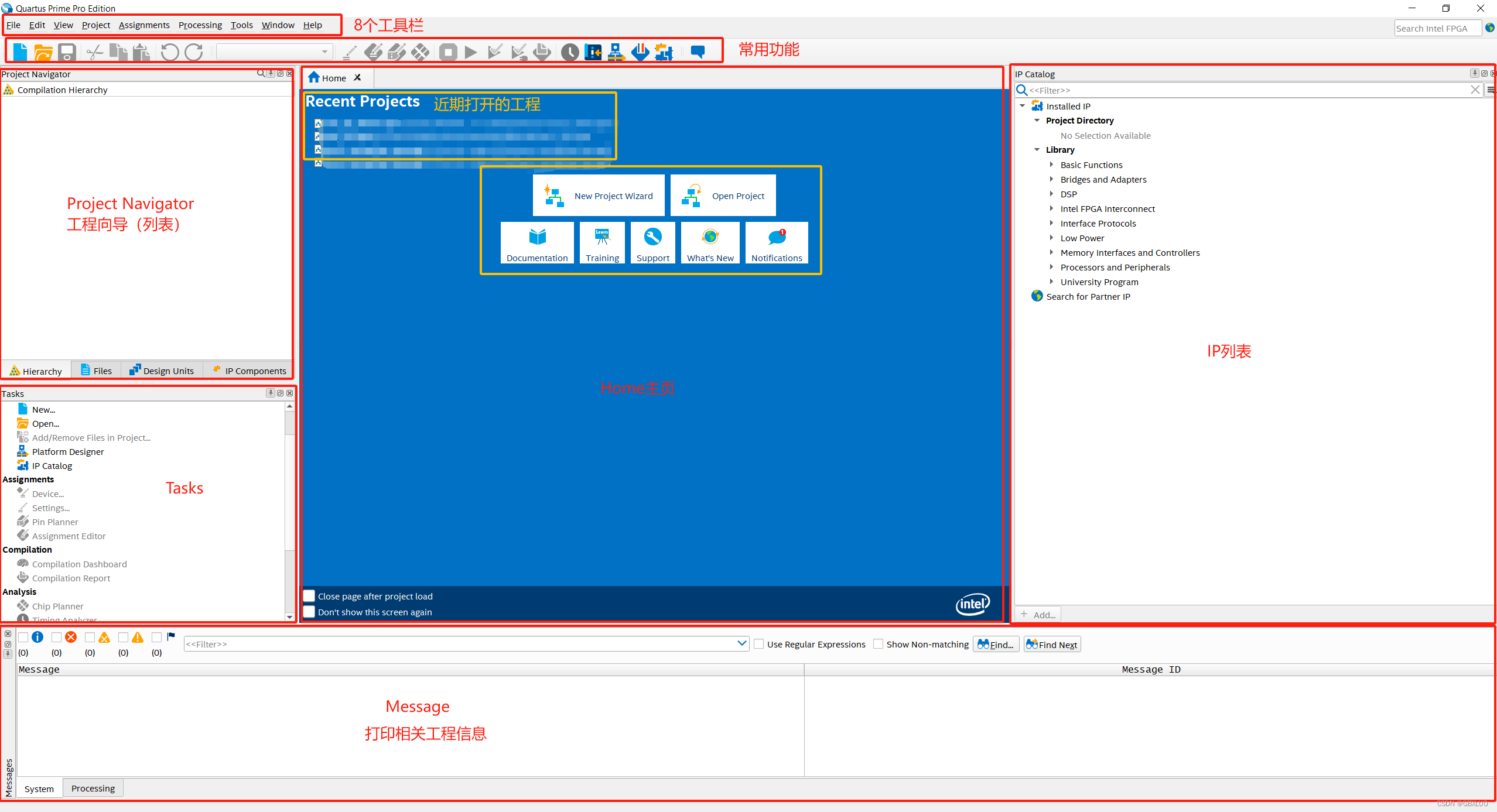

软件界面

默认打开的软件界面如下:

关掉所有能关闭的窗口,剩下的就是一个软件最基本的结构

——GBXLUO语录

从上图可以知道,Quartus可以分为工具栏和常用功能栏,Quartus所有的功能都可以从9个工具栏中找到。

工具栏:File、Edit、View、Project、Assignments、Processing、Tools、Window、Help

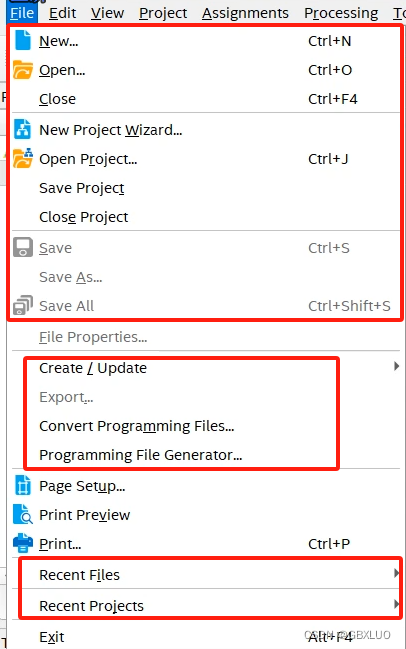

1、File工具栏

这里比较简单,主要是打开/新建工程/文件,这里要注意的是可以快速打开最近的工程,与Home下的Recent Projects相同。

1.1、新建文件/工程、关闭/打开/保存工程等

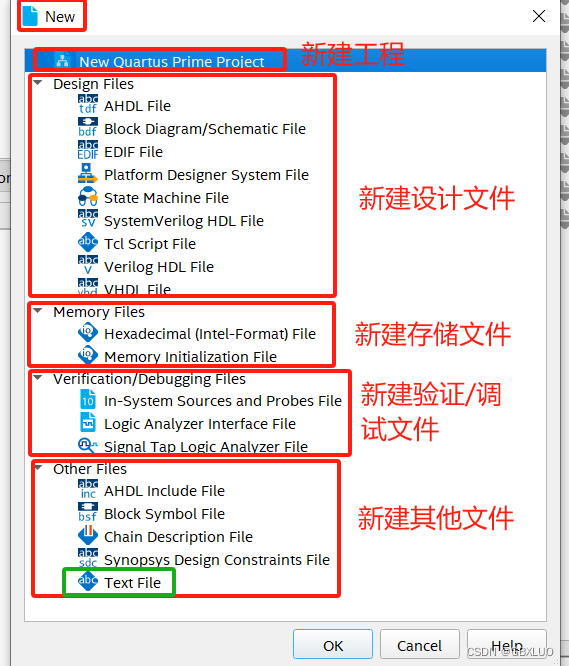

比较简单,但是单击New可以创建很多文件:

新建工程方法 :

参考我这一篇文档:Quartus II 17.1新建一个流水灯

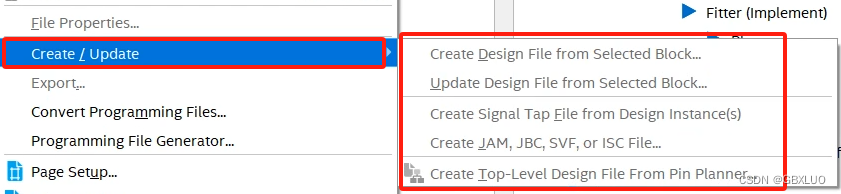

1.2、Create/Update

不常用的Create/Update暂时没用过。

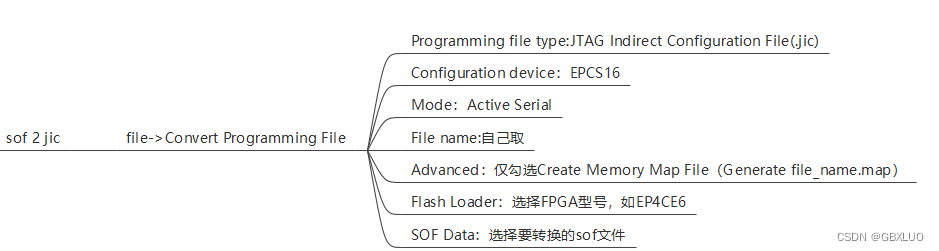

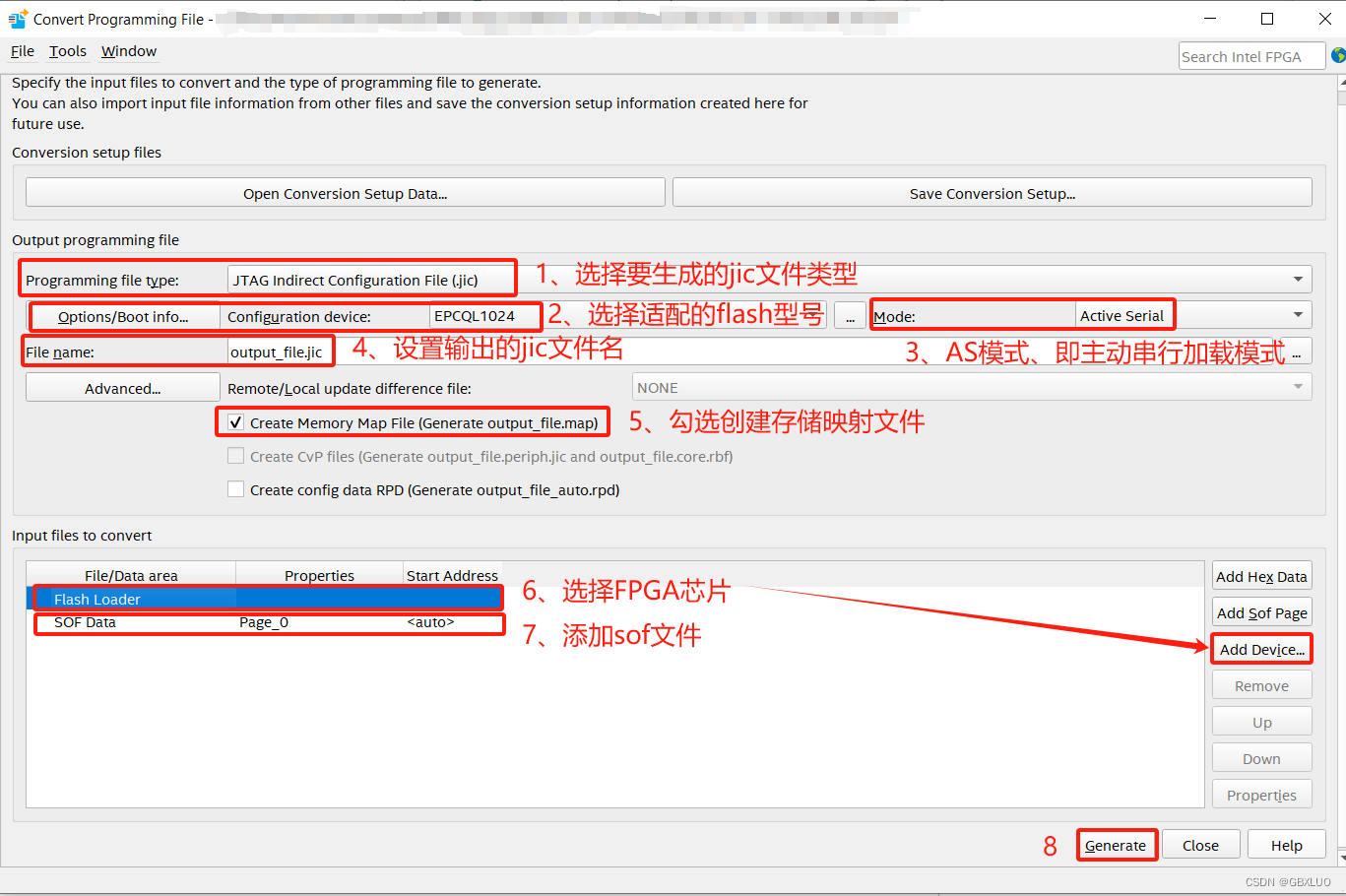

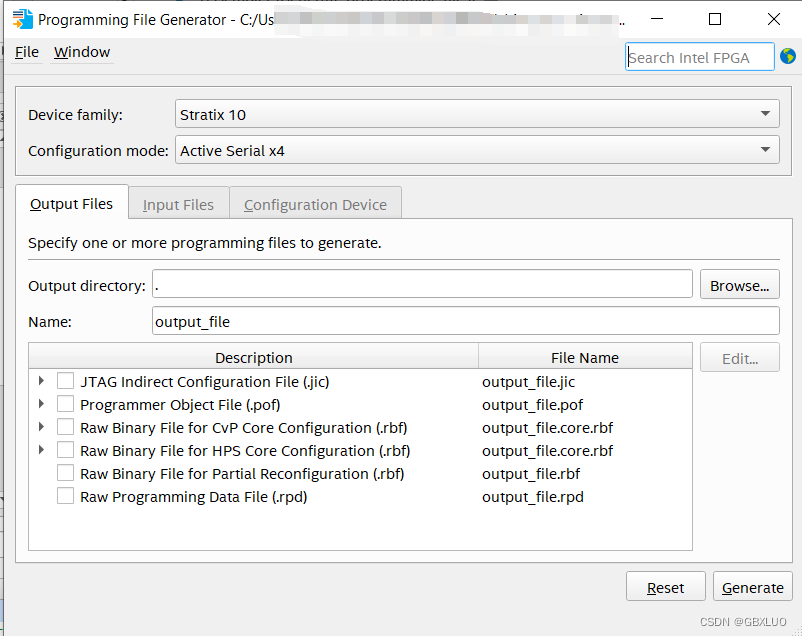

1.3、Convert Programming File:

经常用,将sof文件转换为jic文件,用于下载到板载flash中,下载的sof 文件存于FPGA内部ram资源中,断电即消失。

简单用法如下:

FPGA器件有三类配置下载方式:

1、AS模式(active serial configuration mode,主动串行配置模式):FPGA每次上电时作为控制器,由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,向配置器件主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程配置数据通过FPGA_DATA0引脚送入FPGA,配置数据被同步在FPGA_DCLK上,1个时钟传送1位数据。

2、PS模式(passive serial configuration mode,被动串行配置模式):

由外部计算机或者控制器控制配置过程,通过加强型配置器件(EPC16, EPC8)等配置器件来完成,EPCS作为控制器件,把FPGA当作存储器,把数据写入到FPGA中,实现对FPGA的编程,该模式可以实现对FPGA在线可编程。

3、JTAG模式(Joint Test Action Group,联合测试组):JTAG是直接烧到FPGA里面的,由于是烧写到SRAM中,因此断电后要重烧,AS是烧到FPGA的配置芯片里保存的,每次上电就写到FPGA里。

一般情况下,Cyclone器件应该有两种下载方式,AS和JTAG,AS就是下载.pof文件到EPCS**中,而JTAG是下载.sof文件到FPGA中的SRAM中。

1.4、Programming File Generator-暂时没用过

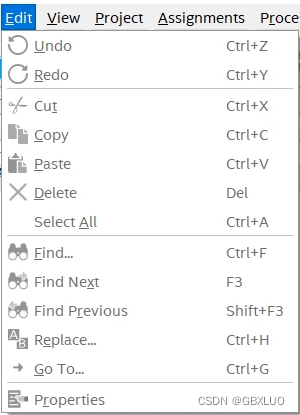

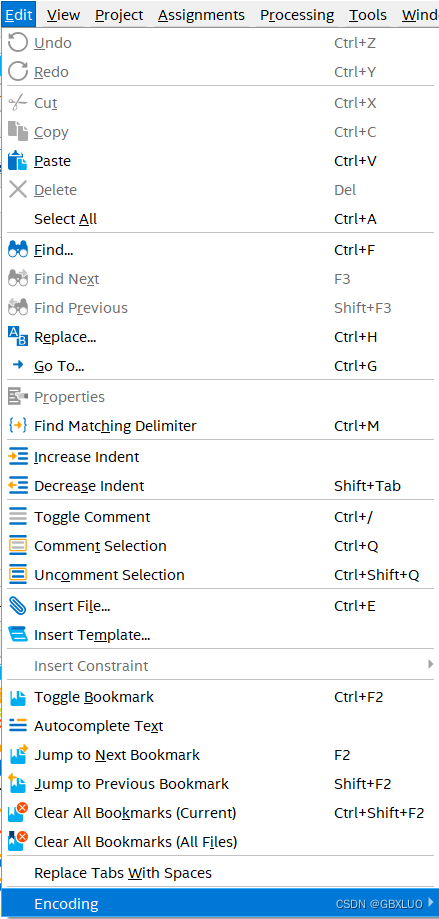

2、Edit-基本可以忽略

用的太少了,基本不用,

不过在使用Quartus自带的文本编辑时,再单击Edit会弹出一大堆东西,如下:

因Quartus自带的文本编辑器用的较少,有需要可以再单独了解。

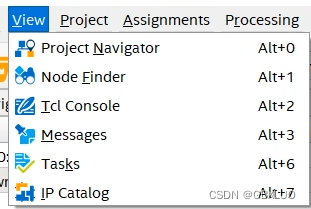

3、View

View是个好东西

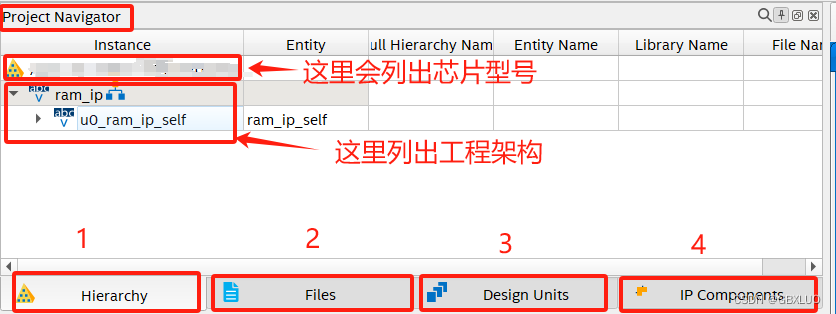

3.1、Project Navigator-工程向导

列出了工程所包含的各个模块,双击即可打开,常用。

Hierarchy:以结构的方式列出工程中的各大V模块(.v模块文件);

Files:列出工程中所有的文件,在Files这里可以添加/删除.v文件;

Design Units,没有关注过,不知有什么用;

IP Components:列出了工程中用到的IP,双击IP可以编辑IP参数。

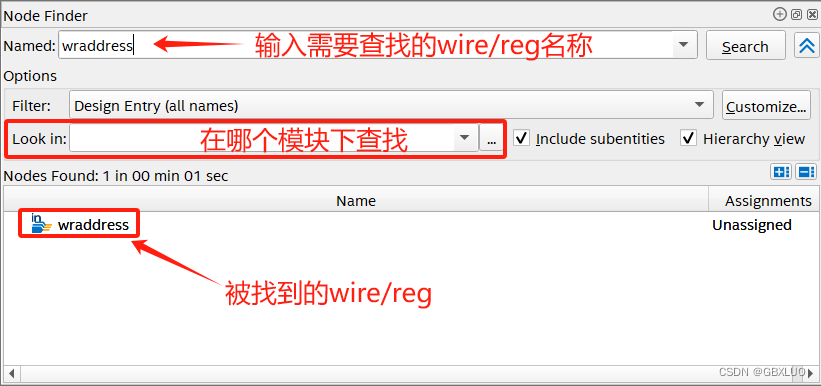

3.2、Node Finder

在这里没有看出来有什么作用,似乎是鸡肋一个。

但是几乎相同的界面在Signal Tap II Logic Analyzer中是很重要的操作。

3.3、Tcl Console

暂时没用过,用过NIOS II Command Shell,一样的功能。

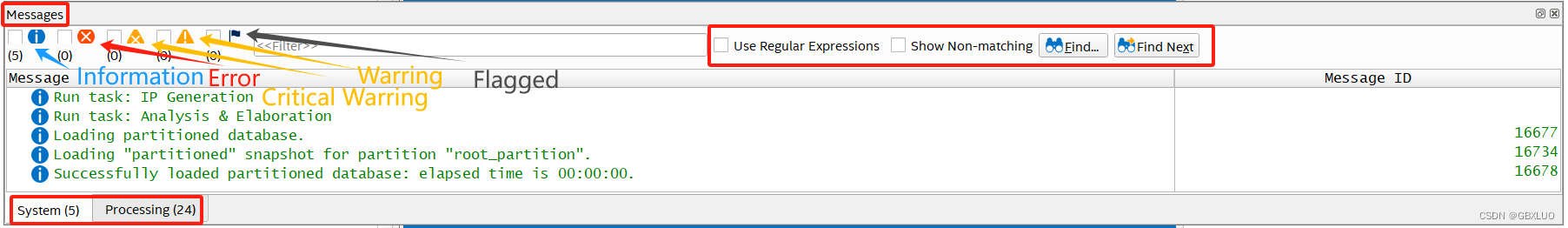

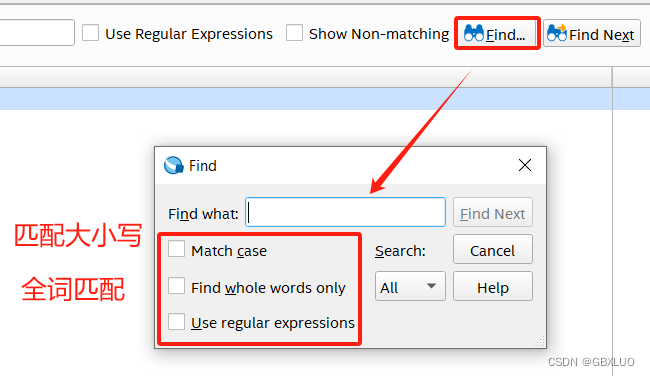

3.4、Messages

Messages窗口打印系统正在/已进行过的信息,特别是工程的编译信息。

有两种方法快速查找信息:

方法一:通过勾选5个小窗格来筛选信息:

从左到右依次是Information、 Error、Critical Warring、Warring、Flagged

方法二、Find方式,输入想要查找的关键词

当然,这两种方法可以一起用。

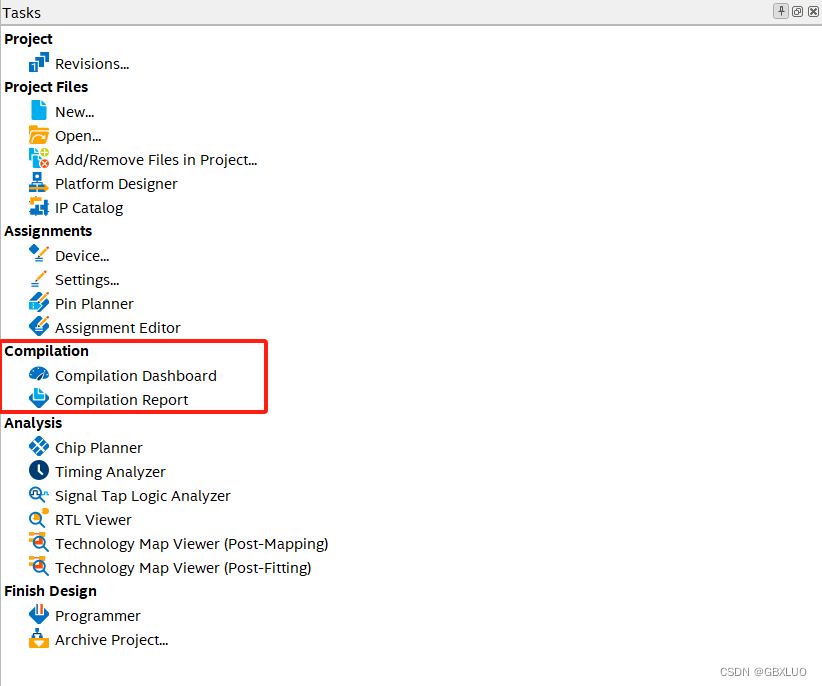

3.5、Tasks

单击即可打开各种任务。

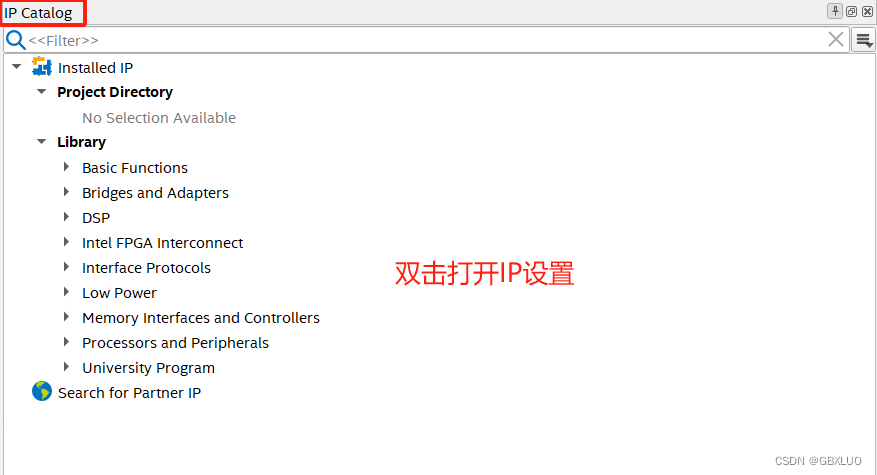

3.6、IP Catalog

编辑IP参数并添加各种IP。如FIFO、RAM、DSP;

此外有一个很重要的功能,生成部分IP的demo,比如DP、HDMI,,,,

4、Project

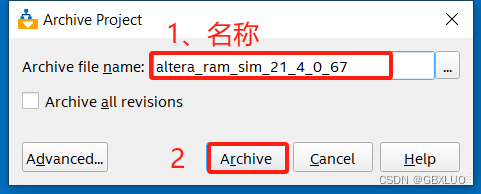

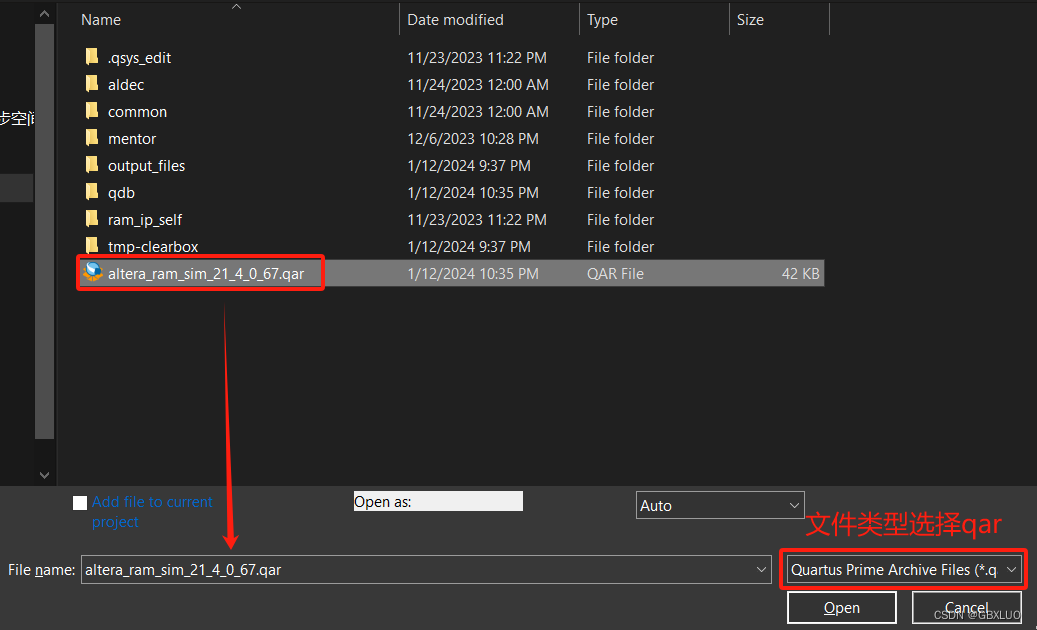

这里,只有Archive Project(打包工程成一个qar文件,方便传输,贼简单)被经常用到,其他均暂未使用。

4.1 Archive Project

怎么打开呢?

用相同的Quartus软件版本打开即可,打开类型选择.qar即可。

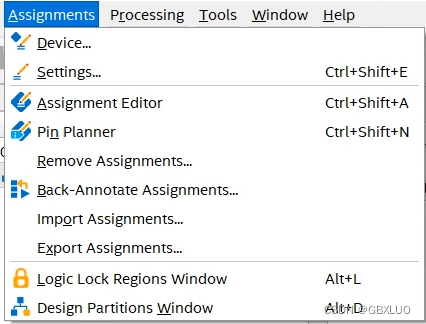

5、Assignments

这里主要就是一些设置了。

暂时没有什么好说的,有空慢慢填充了。

assignment 发音:əˈsaɪnmənt

n.作业,任务;(工作等的)分配,指派;(财产、权利的)转让

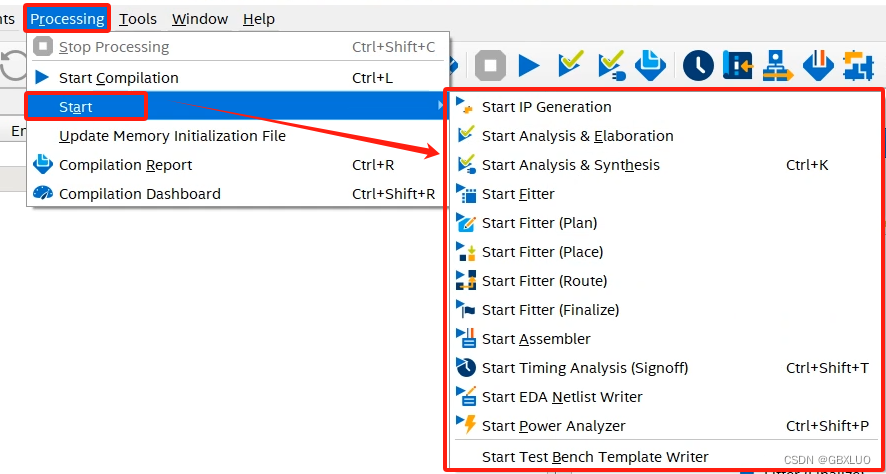

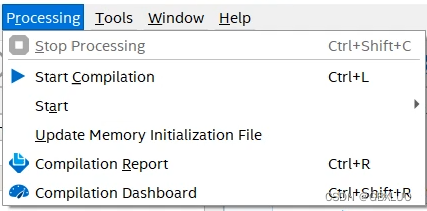

6、Processing

6.1 Start Compilation

开始全编译,会生成sof烧录文件。

6.2、Start

暂时没用过,功能还蛮多。

6.3、Update Memory Initialization File-没用过

6.4、Compilation Report

会生成完成编译后的报告,待补充。

6.5、Compilation Dashboard-编译控制面板

可以单击三角形进行编译。

dashboard 发音:ˈdæʃbɔːd

n.(汽车的)仪表板;<史>(马车上木制或皮制的)挡泥板;总结性表格;网站主页

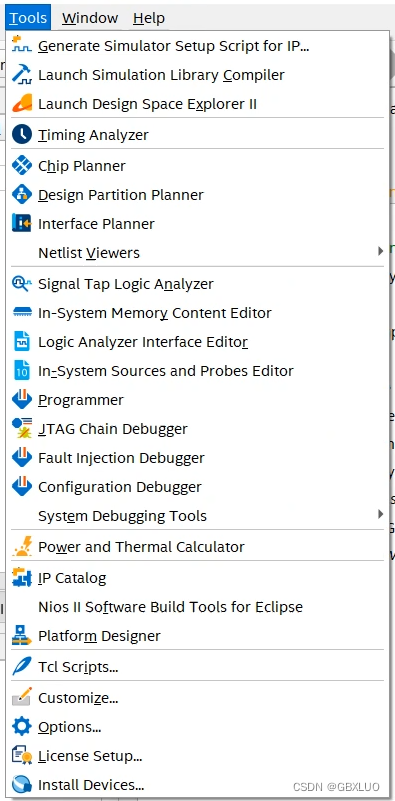

7、Tools

功能太多太强,有很多还没用着。每一个功能单独拎出来都能水一篇。

7.1 Generate Simulator Setup Script for IP

参考我这一篇文档:Quartus II + Modelsim 脚本仿真

7.x Chip Planner

待补充

7.x Signal Tap Logic Analyzer

参考我这一篇文档:Quartus的Signal Tap II的使用技巧

7.x In-System Sources and Probes Editor

待补充

7.x Programmer

待补充

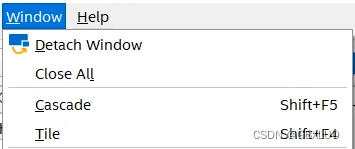

8、Window

8.1 Detach Window:就是将选中的窗口悬浮,自由拖动

相反的则是Attach Window;

detach 发音:dɪˈtætʃ

v.拆下,使分离;脱离,摆脱;派遣,分派

attach 发音:əˈtætʃ

v.系上,贴上,连接;附上(附件);赋予,认为……具有; 和……在一起,缠着; 附带(条件);附属,依附;与……有关联;委派;扣押(债务人或其财产);使依恋

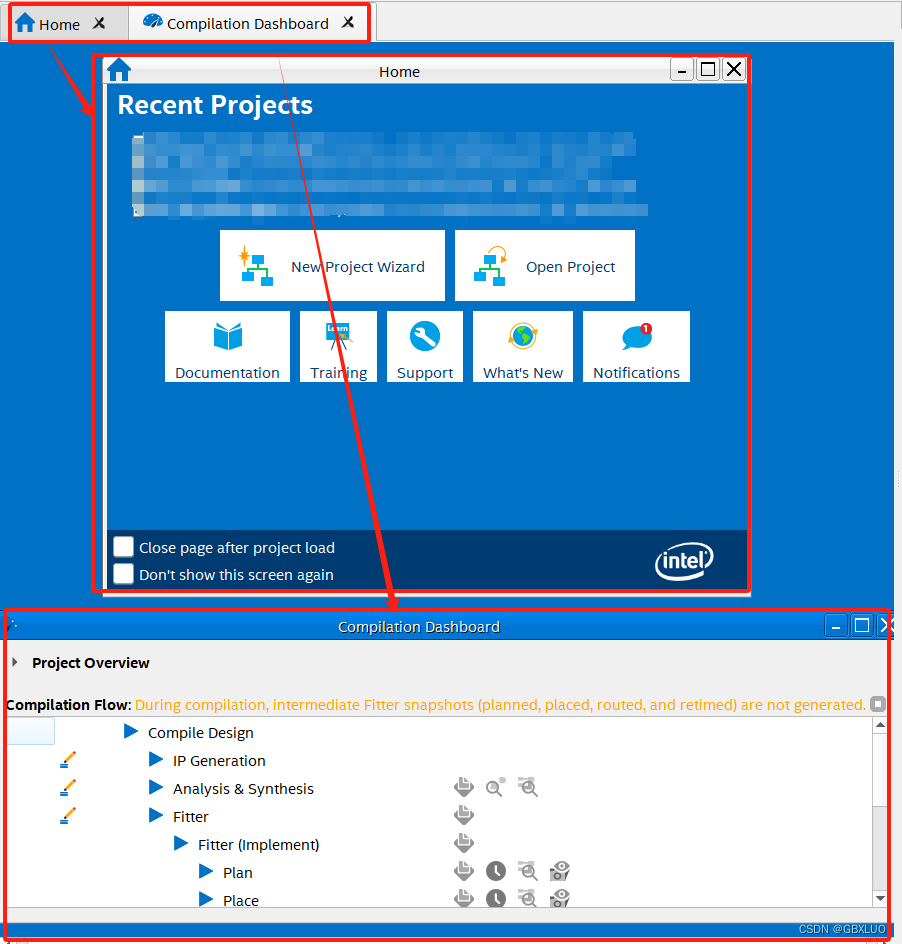

8.2 Close All:关闭除Home窗口外的所有窗口

在Window窗口下,关闭除Home窗口外的所有窗口,如下图:

Close All这个按键 可以关闭Compilation Dashboard窗口,但关闭不了Home窗口(可以手动关闭Home窗口)。

8.3 Cascade-所有该界面下的Home 与Compilation Dashboard全部悬浮

Cascade 发音:kæˈskeɪd

n.小瀑布(尤指大瀑布的一支);倾泻,流注;瀑布状物;倾泻(或涌出)的东西;(很快发生的)一连串事情;(尤指信息或知识等的)连续传递过程;(一个过程中前一个引发后一个的)连续阶段,一系列装置

v.(水)倾泻,流注;大量落下,垂下;连续传递,传授;使(装置,物品)串联

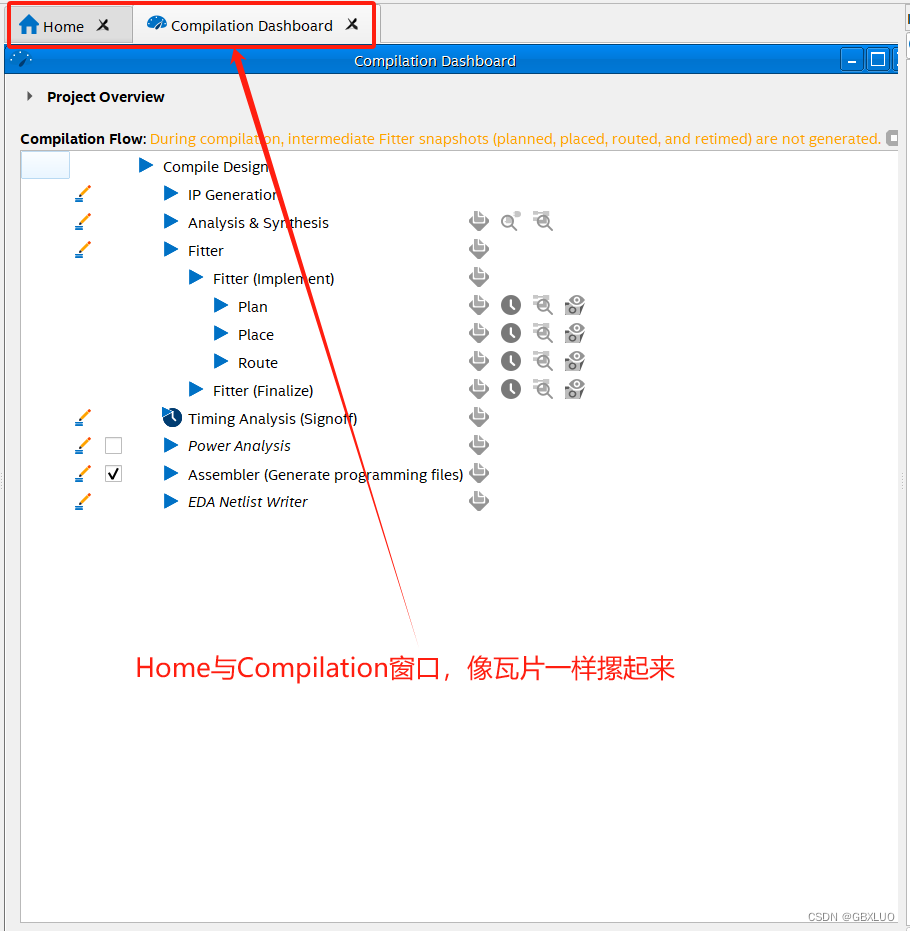

8.4 Tile

tile 发音:taɪl

n.(贴墙或铺地用的)瓷砖,地砖;(铺屋顶的)瓦,瓦片;(拼字游戏、麻将等牌戏中的)(一张)牌;(棋盘游戏的)棋子;(数)平铺

v.铺瓦,铺砖;(计算机)平铺(窗口)

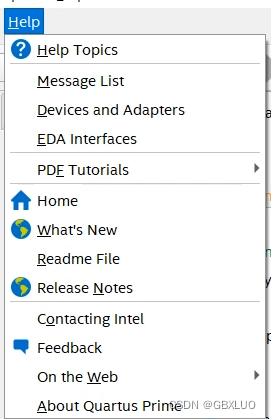

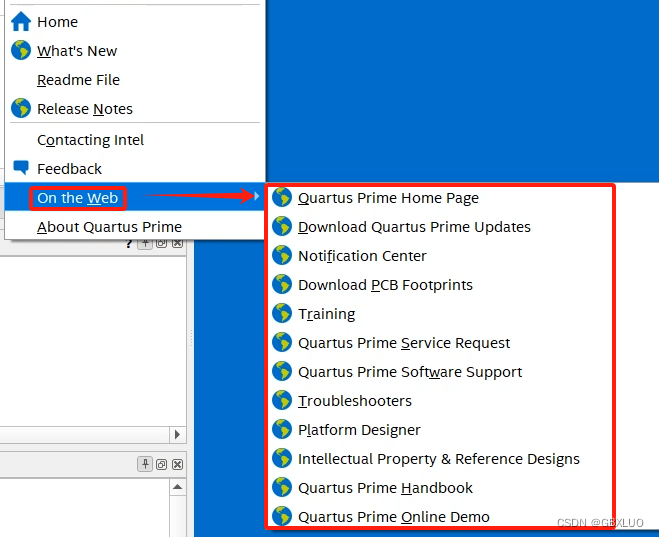

9、Help-与官网联系紧密

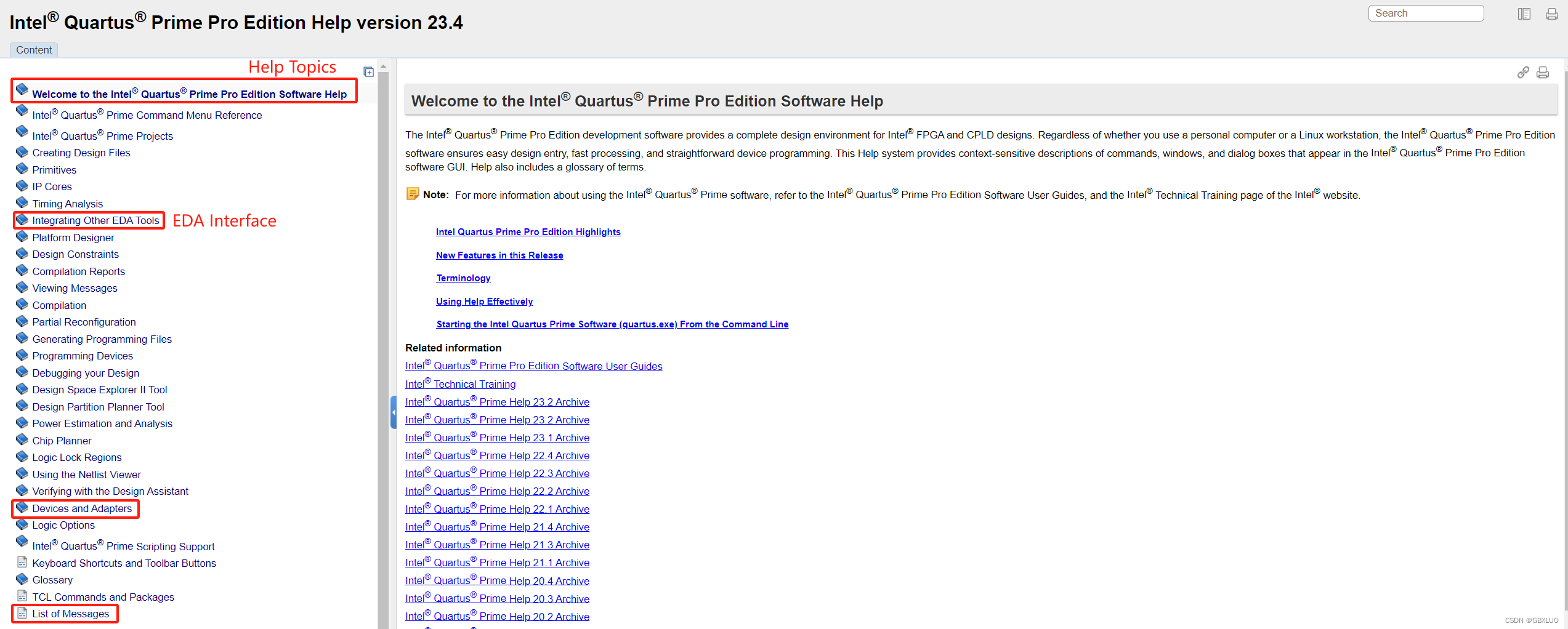

9.1 Help相关文档

上图圈中的4个选项都在Intel® Quartus® Prime Pro Edition Help version 23.4中,

官方网址:Intel® Quartus® Prime Pro Edition Help version 23.4

注意:这里还有一个TCL Commands and Packages,可以查阅tcl脚本命令。

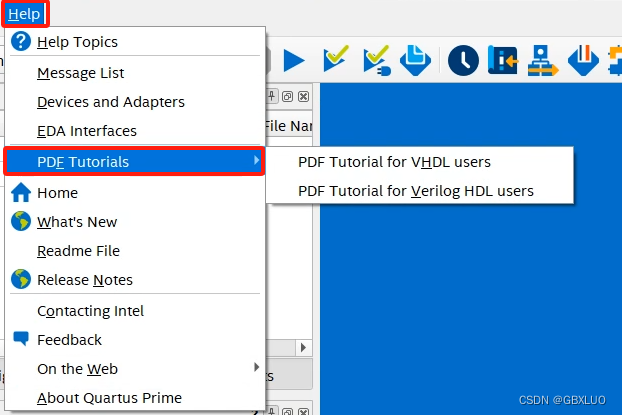

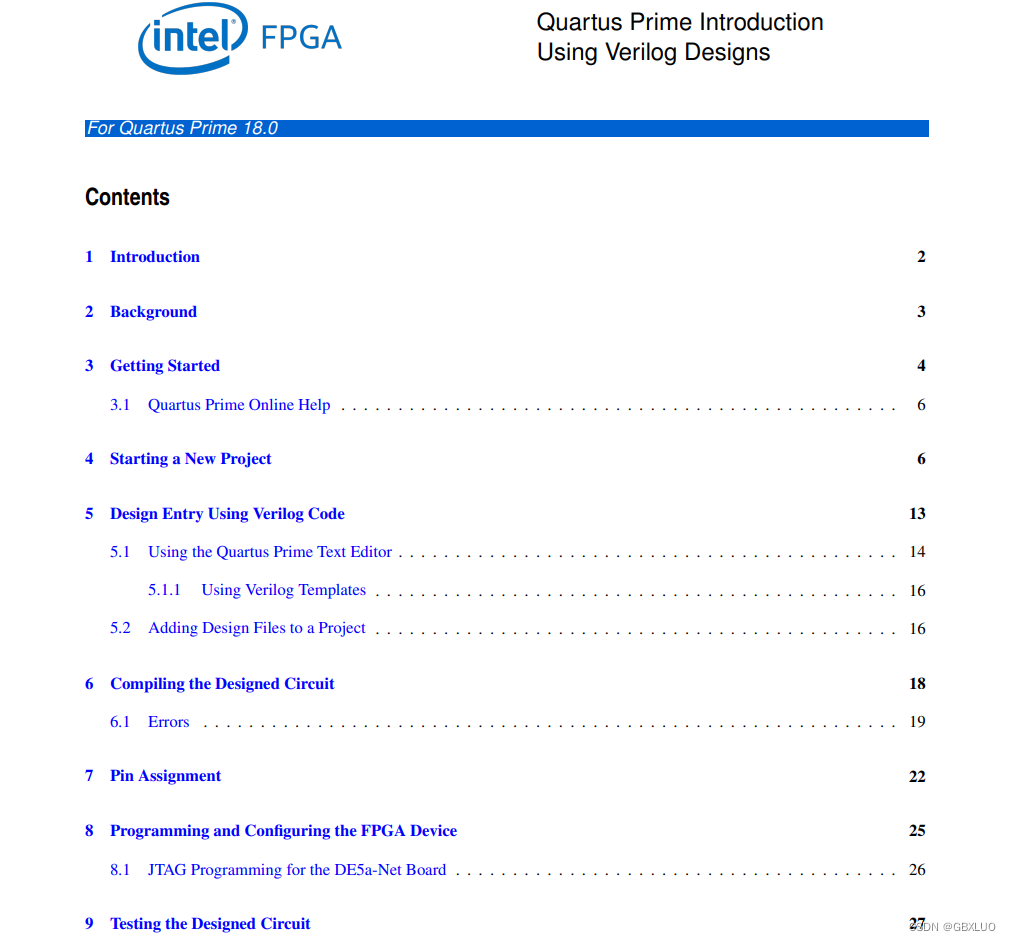

9.2、PDF Tutorials

点击PDF Tutorial for Verilog HDL users,打开后如下:方便快速入门。

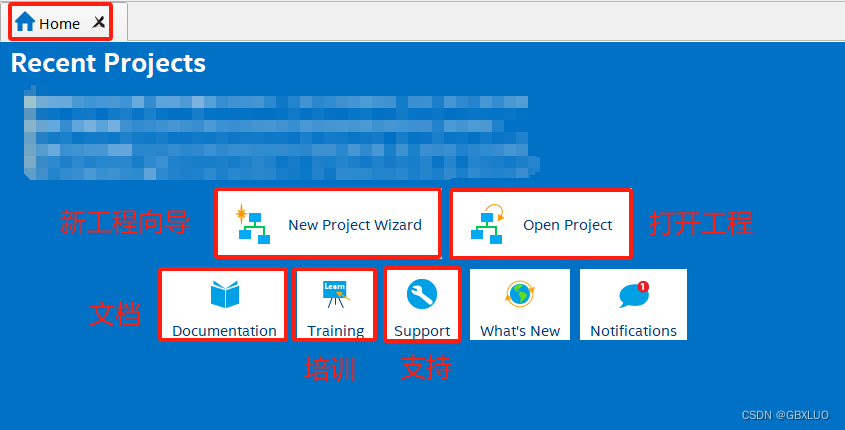

9.3、Home

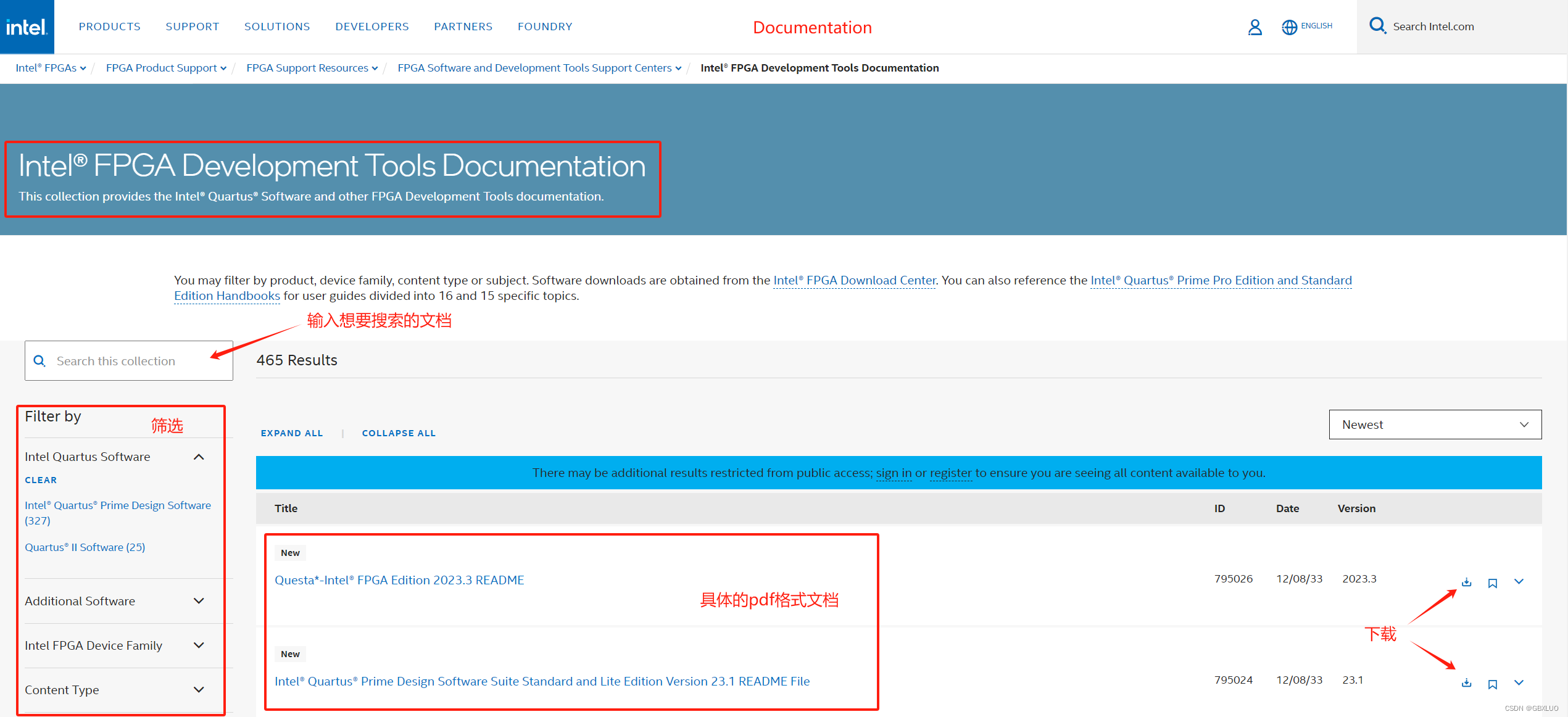

9.3.1 Documentation

可以在如下网站查找相关pdf格式的文档查阅。

官方网址:Intel® FPGA Development Tools Documentation

9.3.2 Training

还没用过,看起来这些培训资料还行。

官方网址:Intel® FPGA Technical Training

9.3.3 Support

很多好东西,如下:

官方网址:Intel® FPGA Support Resources

9.4 其他

9.4.1 On the Web

这里注意有支持PADS和Allergo的PCB封装库。

参考链接:

FPGA程序烧写方式——AS PS JTAG_as模式不过fpga吗-CSDN博客