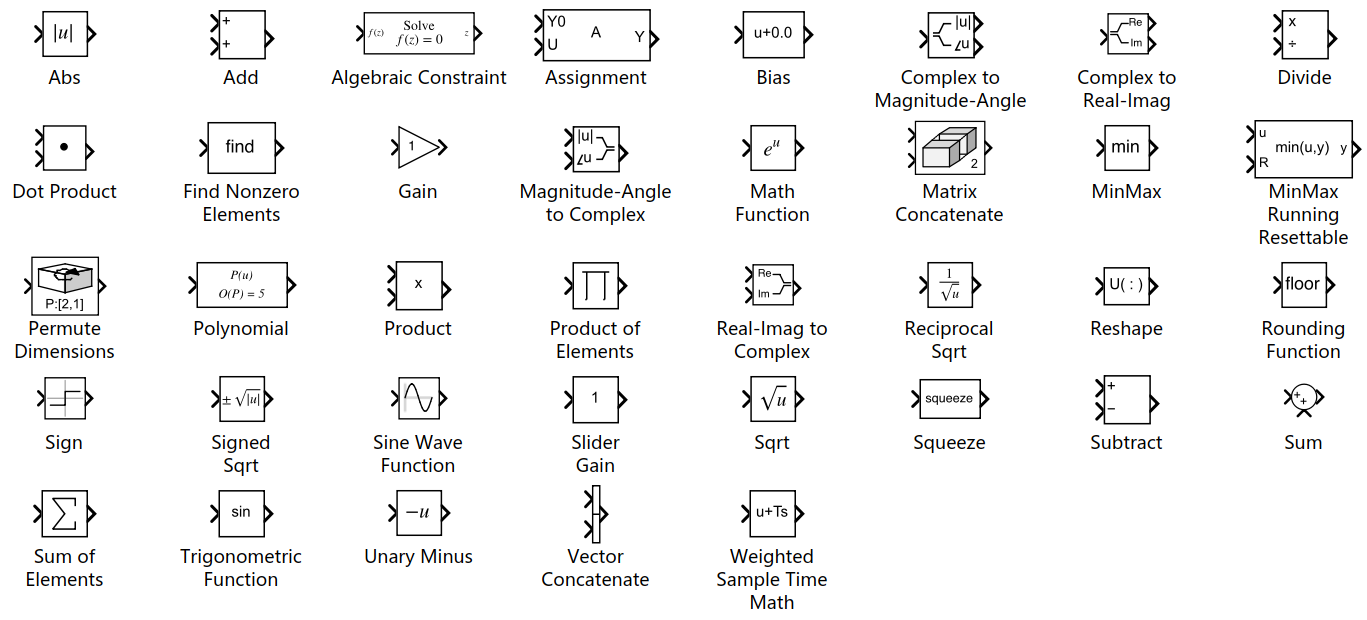

Simulink模块说明

Simulink库

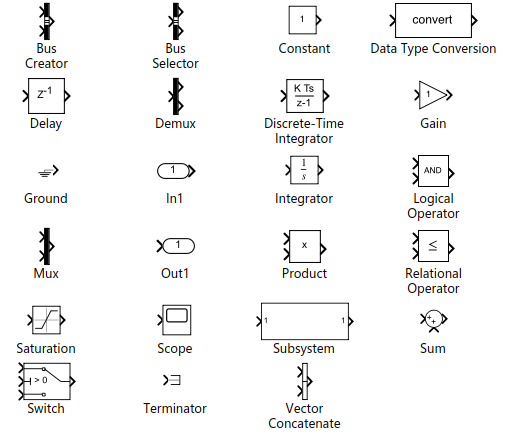

Commonly Used Blocks

Bus Creator

将一组输入元素合并成一条总线

**输入:**要包含在总线中的输入元素。

**输出:**由合并的输入元素组成的输出总线,指定为虚拟或非虚拟总线。

Bus Selector

Bus Selector 模块输出您从输入总线选择的元素。该模块可以单独输出所选的各元素或在一个新的虚拟总线中输出所选元素。

**输入:**输入总线,可以是虚拟总线,也可以是非虚拟总线。对于总线数组,您必须使用 Selector 模块来选择要与 Bus Selector 模块结合使用的总线。

**输出:**输入总线的所选总线元素。该模块自上而下地对每个输出元素使用一个单独的端口。

Constant

生成实数或复数常量值信号。使用此模块提供常量信号输入。

此模块的输出与常量值参数具有相同的维度和元素。如果为此参数指定向量,即您希望模块将其解析为向量,请选中将向量参数解释为一维向量复选框。否则,如果为常量值参数指定了向量,模块会将该向量视为一个矩阵。

**输出:**常量值,指定为实数或复数值标量、向量、矩阵或 N 维数组。

Data Type Conversion

Data Type Conversion 模块可将任何 Simulink® 数据类型的输入信号转换为您指定的数据类型。

**输入:**输入信号,指定为标量、向量、矩阵或 N 维数组。输入可以是任何实数或复数值信号。如果输入为实数,则输出也是实数。如果输入为复数,则输出也是复数。

**输出:**输出信号,转换为您指定的数据类型,具有与输入信号相同的维度。

Delay

Delay 模块会在一段延迟之后再输出模块的输入。此模块根据延迟长度参数的值来确定延迟时间。

输入:

- u - 数据输入信号:根据参数设置延迟的输入数据信号。

- d - 延迟长度:指定为从输入端口继承的延迟长度。当您对延迟长度:源参数选择“输入端口”时启用。

- Enable - 使能信号:使能信号,用于启用或禁用模块的执行。要创建此端口,请选择显示使能端口参数。

- 外部重置信号:将模块的执行重置为初始状态的外部信号。要创建此端口,请选择外部重置参数。

- x0 - 初始条件:指定为从输入端口继承的初始条件。当您对初始条件:源参数选择“输入端口”时启用。

输出:输出信号,它是按参数延迟长度指定的时间长度延迟后的输入信号。

Demux

Demux 模块提取输入向量信号的分量,再将它们输出为单独的信号。输出信号端口从上到下排列。

**输入:**Demux 模块从中选择标量信号或更小向量的向量输入信号。

**输出:**输出从输入向量中提取的信号。输出信号端口从上到下排列。

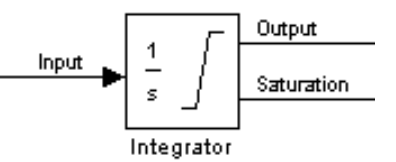

Discrete-Time Integrator

使用 Discrete-Time Integrator 模块替代 Integrator 模块来创建纯离散模型。

**输入:**输入信号,指定为标量、向量或矩阵。

IC - 状态的初始条件,指定为有限标量、向量或矩阵。

**输出:**Port_1 - 输入的离散时间积分或累积,指定为标量、向量或矩阵。

Port_2 - 饱和输出。指示状态何时受限的信号,指定为标量、向量或矩阵。信号具有以下三个值之一:

- 1 表示正在应用上限。

- 0 表示积分不受限制。

- -1 表示正在应用下限。

Port_3 状态输出。模块状态,输出为标量、向量或矩阵。默认情况下,模块将此端口添加到模块图标的顶部。

积分方法或累积方法:

此模块可以使用前向欧拉、后向欧拉或梯形法对信号进行积分或累积。假定 u 为输入,y 为输出,x 为状态。对于给定步长 n,Simulink 将更新 y(n) 和 x(n+1)。在积分模式下,T 是模块的采样时间(如果是触发采样时间,则是 delta T)。在累积模式下,T = 1。模块采样时间决定计算输出的时间,而不是输出值。K 是增益值。值根据上限或下限进行剪切。

前向欧拉方法

前向欧拉方法(默认值),也称为正向矩形或左手逼近方法

该软件将 1/s 近似为 T/(z-1)。模块在第 n 个时间步的输出的表达式为:

x(n+1) = x(n) + K*T*u(n)

y(n) = x(n)

模块按照以下时间步计算输出:

Step 0: y(0) = IC (clip if necessary)x(1) = y(0) + K*T*u(0)Step 1: y(1) = x(1)x(2) = x(1) + K*T*u(1)Step n: y(n) = x(n)x(n+1) = x(n) + K*T*u(n) (clip if necessary)

使用此方法时,输入端口 1 没有直接馈通。

后向欧拉方法

后向欧拉方法,也称为反向矩形或右手逼近方法

该软件将 1/s 近似为 Tz/(z-1)。模块在第 n 个时间步生成的输出的表达式为:

y(n) = y(n-1) + KT*u(n).

假设 x(n) = y((n)-1)。模块按照以下时间步计算输出。

- 如果触发子系统和函数调用子系统的参数初始条件设置设置为“输出”或“自动”:

Step 0: y(0) = IC (clipped if necessary)x(1) = y(0)

- 如果非触发子系统的参数初始条件设置设置为 “”:

Step 0: x(0) = IC (clipped if necessary)x(1) = y(0) = x(0) + K*T*u(0)Step 1: y(1) = x(1) + K*T*u(1)x(2) = y(1)Step n: y(n) = x(n) + K*T*u(n)x(n+1) = y(n)

使用此方法时,输入端口 1 具有直接馈通。

梯形法

对于此方法,本软件将 1/s 近似为 T/2*(z+1)/(z-1)。

当 T 固定时(等于采样周期),计算输出的表达式为:

x(n) = y(n-1) + K*T/2*u(n-1)

y(n) = x(n) + K*T/2*u(n)

- 如果触发子系统和函数调用子系统的参数初始条件设置设置为“输出”或“自动”:

Step 0: y(0) = IC (clipped if necessary)x(1) = y(0) + K*T/2*u(0)

- 如果非触发子系统的参数初始条件设置设置为 “”:

Step 0: x(0) = IC (clipped if necessary)y(0) = x(0) + K*T/2*u(0)x(1) = y(0) + K*T/2*u(0)Step 1: y(1) = x(1) + K*T/2*u(1)x(2) = y(1) + K*T/2*u(1)Step n: y(n) = x(n) + K*T/2*u(n)x(n+1) = y(n) + K*T/2*u(n)

这里,x(n+1) 是下一个输出的最佳估计值。它与状态的不同之处在于,x(n) 不等于 y(n)。

使用此方法时,输入端口 1 具有直接馈通。

当 T 为变量时

当 T 是变量时(例如,从触发时间获得),模块将按照以下时间步计算输出。

- 如果触发子系统和函数调用子系统的参数初始条件设置设置为“输出”或“自动”:

Step 0: y(0) = IC (clipped if necessary)x(1) = y(0)

- 如果非触发子系统的参数初始条件设置设置为 “”:

Step 0: x(0) = IC (clipped if necessary)x(1) = y(0) = x(0) + K*T/2*u(0)Step 1: y(1) = x(1) + T/2*(u(1) + u(0))x(2) = y(1)Step n: y(n) = x(n) + T/2*(u(n) + u(n-1))x(n+1) = y(n)

Gain

Gain 模块将输入乘以一个常量值(增益)。输入和增益可以是标量、向量或矩阵。

**输入:**Gain 模块接受实数或复数值标量、向量或矩阵输入。Gain 模块支持定点数据类型。如果 Gain 模块的输入为实数,增益为复数,则输出为复数。

**输出:**Gain 模块的输出是输入乘以常量增益值。当 Gain 模块的输入为实数且增益为复数时,输出为复数。

Ground

接地

**输出:**Ground 模块输出具有零值的标量信号,其数据类型与所连接的端口相同。

In1

Inport 模块将信号从系统外部链接到系统内。

**输出:**通过输入端口流入系统的输入信号。

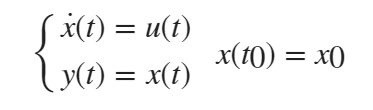

Integrator

通过输入端口流入系统的输入信号。

输入:

- 被积函数信号(double)

- 外部重置信号:将状态重置为初始条件。要启用此端口,请启用外部重置参数。

- x0 - 初始条件:根据外部信号设置模块状态的初始条件。要启用此端口,请将初始条件参数设置为“外部”。(double)

输出:

- 输出信号(double)

- 显示输出饱和:指示状态何时受到限制。当积分由指定的饱和上限限制时,信号的值为 1。当信号由饱和下限限制时,信号值为 -1。当积分介于饱和限制之间时,信号值为 0。(double)

- 状态:输出模块的状态。通过启用显示状态端口参数来启用此端口。(double)

Logical Operator

Logical Operator 模块对其输入执行指定的逻辑运算。输入值为非零值时为 true (1),为零时则为 false (0)。

Mux

将相同数据类型和复/实性的输入信号合并为虚拟向量

- 输入:要包含在复路信号中的输入信号,指定为标量或向量。Mux 模块的输入信号可以是标量和向量的任意组合,但它们必须具有相同的数据类型和复/实性。

- 输出:由合并的输入信号组成的输出复路信号,以向量形式返回。输出复路信号的元素按照输入信号的端口顺序排列。

out1

为子系统或外部输出创建输出端口

输入:通过输出端口流向外部子系统或模型的输入信号。

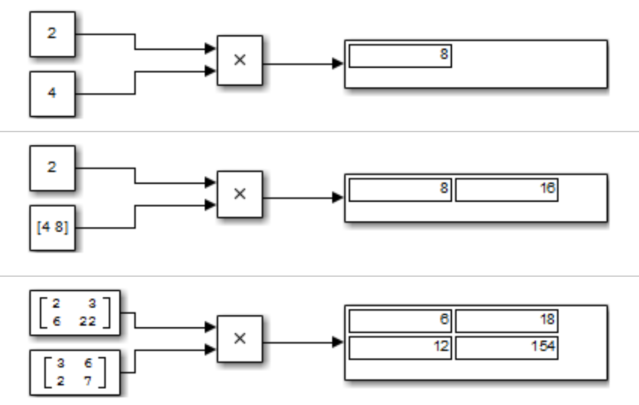

Product

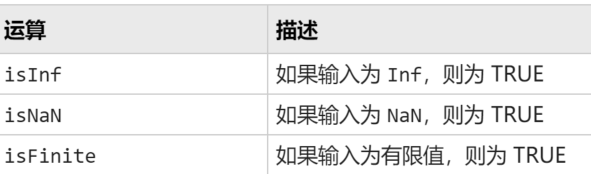

标量和非标量的乘除运算或者矩阵的乘法和逆运算

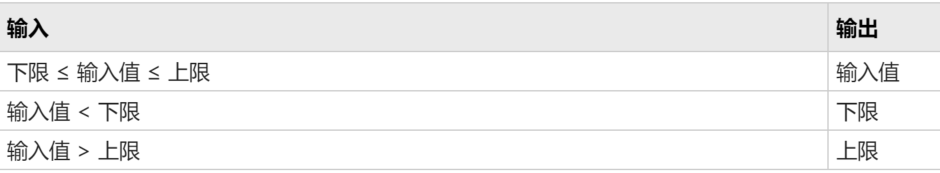

Relational Operator

双输入模式

单输入模式

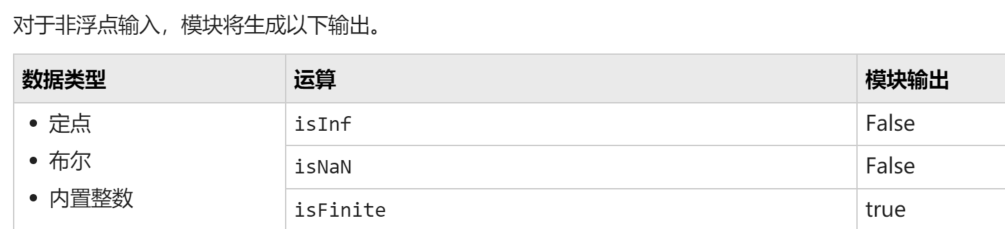

Saturation

将输入信号限制在饱和上界和下界值之间

Scope

Subsystem

对各模块进行分组以创建模型层次结构

- 输入:在子系统中放置一个 Inport 模块会向 Subsystem 模块添加一个外部输入端口。端口标签与 Inport 模块的名称相匹配。使用 Inport 模块可以从局部环境中获取信号。

- 输出:在子系统中放置一个 Outport 模块会从 Subsystem 模块添加一个输出端口。Subsystem 模块上的端口标签是 Outport 模块的名称。使用 Outport 模块可以向局部环境发送信号。

Sum

输入信号的加减运算

Switch

Switch 模块根据第二个输入的值,传递第一个输入或第三个输入信号。第一个和第三个输入是数据输入。第二个输入是控制输入。可以使用首个输入传递条件和阈值参数指定模块传递第一个输入的条件。

Terminator

终端

使用 Terminator 模块终止输出端口未连接其他模块的模块。如果您运行的仿真中有一些模块的输出端口未连接任何模块,Simulink® 将发出警告消息。使用 Terminator 模块终止这些模块,可以防止出现此类警告消息。

Vector Concatenate

Vector Concatenate 和 Matrix Concatenate 模块串联输入信号,以创建一个非虚拟输出信号,其元素位于内存中的连续位置。

Continuous库

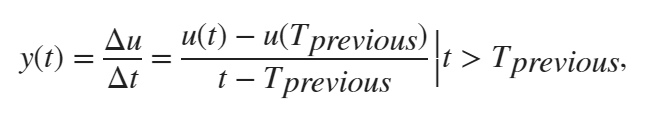

Derivative

Derivative 模块可近似计算输入信号 u 相对于仿真时间 t 的导数。方法是计算数值差异 Δ_u_/Δ_t_,其中 Δ_u_ 是输入值的变化,Δ_t_ 是自上一个仿真(主要)时间步以来的时间变化。

此模块接受一个输入并生成一个输出。模块的初始输出为零。具体的计算原理为:

其中 t 是当前仿真时间,Tprevious 是上次仿真输出的时间。后者与上次主时间步的时间相同。

Derivative 模块的输出可能对整个模型的动态比较敏感。输出信号的准确度取决于仿真中采用的时间步长的大小。步长越小,此模块的输出曲线就越平滑和准确。但是,与具有连续状态的模块不同,当此模块的输入快速变化时,求解器不会采用较小的步长。根据驱动信号和模型的动态,此模块的输出信号可能包含意外波动。这些波动主要是由驱动信号输出和求解器步长导致的。由于存在这种敏感度,电路模型中最好采用Integrator模块而不是Derivative模块。

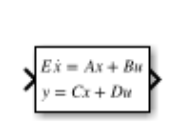

Descriptor State-space

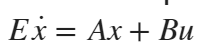

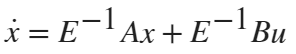

建立线性隐式系统模型:

E是系统的质量矩阵(mass matrix)。当E是非奇异矩阵时,其可逆,故可将其写为显式形式:

然后使用State-space模块建模。当E是奇异矩阵时,方程中不存在系统因变量的一个或多个导数。这些变量称为代数变量。包含这些代数变量的微分方程称为代数微分方程。它们的状态方程表示为:

- x:状态向量

- u:输入向量

- y:输出向量

输入和输出变量的数据Type为’double’。

Entity Transport Delay

实体(entity)传输延迟块将实体延迟一段时间,称为传输延迟。第一个输入是在速度随时间变化的恒定长度表面上从点A传输到点B的实体。第二个输入的值是瞬时延迟。

表面的速度是瞬时延迟的倒数。瞬时延迟与速度的乘积恒等于1。

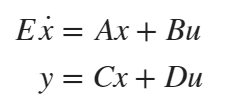

First Order Hold

FOH模块输出其输入的连续分段线性逼近。使用 First Order Hold 模块将采样的离散信号转换为连续信号,而不触发求解器重置。

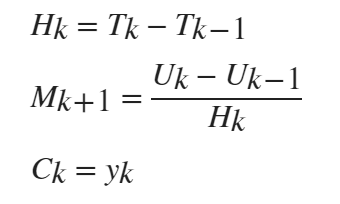

慢速算法(避免过冲法)

慢速或低通算法执行的线性外插可以描述为:

快速算法(最小化误差法)

快速或高通算法执行的线性外插可以描述为:

快速算法通过在模块的更新方法期间尝试预测下一个输入来最小化误差。模块的预测输出中的误差减少与用于过冲输入信号的趋势之间进行折衷。

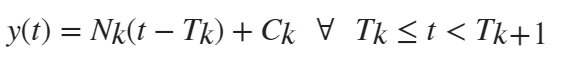

Integrator

Integrator 模块输出其输入信号相对于时间的积分值。模块动态由以下方程指定:

限制积分

此操作会使该模块起到限量积分器的作用。当输出达到界限时,积分操作将关闭以防止积分饱和。

- 1 表示正在应用上限。

- 0 表示积分不受限制。

- -1 表示正在应用下限。

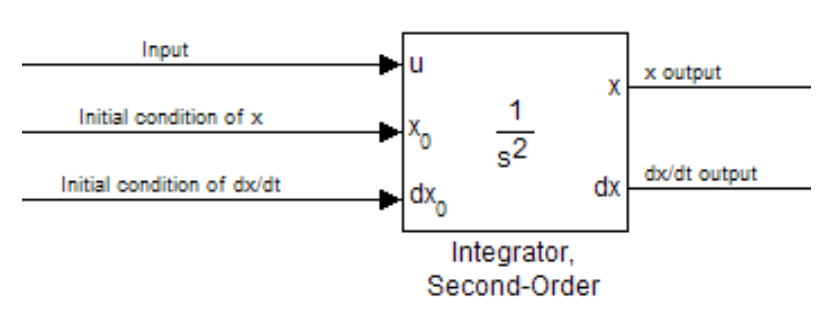

Second-Order Integrator

Second-Order Integrator 模块和 Second-Order Integrator Limited 模块用来求解器二阶初始值问题:

其中 u 是系统的输入信号。因此,此模块是一个动态系统,它具有两个连续状态:x 和 dx/dt。

Second-Order Integrator Limited

Second-Order Integrator Limited 模块除了默认情况下基于指定的上限和下限值来限制状态外,它与 Second-Order Integrator 模块完全相同。

Discrete PID Controller

Discrete PID Controller 模块实现一个 PID 控制器(PID、PI、PD、仅 P 或仅 I)。此模块的输出是输入信号、输入信号积分和输入信号导数的加权和。权重为比例、积分和导数增益参数。通过一阶极点筛选导数操作。要检查模块及其可变子系统的内部结构体,请右键点击该模块,然后选择封装 > 查看封装内部。

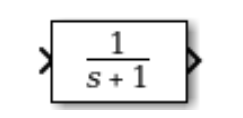

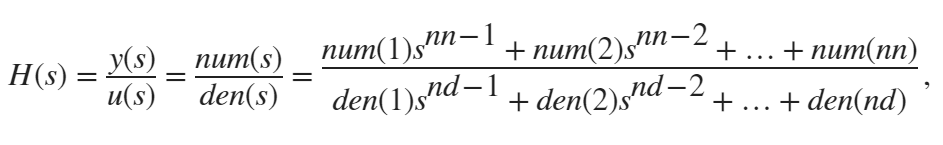

Transfer Fcn

Transfer Fcn 模块通过拉普拉斯域变量 s 的传递函数为线性系统建模。此模块可为单输入单输出 (SISO) 和单输入多输出 (SIMO) 系统建模。

传递函数

其中 u 和 y 分别代表系统输入和输出,nn 和 nd 分别是分子和分母系数。num(s) 和 den(s) 包含分子和分母的 s 降幂系数。

注意:分母的阶必须大于或等于分子的阶。对于多输出系统,所有传递函数具有相同的分母,而所有分子具有相同的阶次。

Transport Delay

Transport Delay 模块可按指定的时间量延迟输入。可使用此模块实现时滞的仿真。此模块的输入应为连续信号。

在仿真开始时,模块输出初始输出参数,直到仿真时间超过时滞参数。然后,模块开始生成延迟的输入。在仿真期间,模块将输入点和仿真时间存储在缓冲区中。可通过初始缓冲区大小参数指定此大小。

如果需要某个时间的输出,而存储的输入值没有对应的时间,模块会在点之间进行线性插值。当延迟小于步长时,模块会根据最后一个输出点外插,这可能会导致结果不准确。因为模块没有直接馈通,无法使用当前输入来计算输出值。例如,假定一个定步长仿真的步长为 1,当前时间为 t = 5。如果延迟为 0.5,模块必须在 t = 4.5 时生成点。因为最新存储的时间值是 t = 4,模块将执行正向外插。

Transport Delay 模块不会对离散信号进行插值。相反,模块会返回所需时间处的离散值。

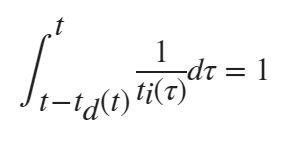

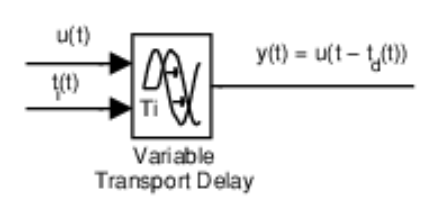

Variable Time Delay/ Variable Transport Delay

在此模式中,当前时间步的模块输出等于之前的时间步(等于当前时间减去传输延迟)的数据(顶部或左侧)输入的值。

y ( t ) = u ( t − t d ( t ) ) y(t)=u(t-t_d(t)) y(t)=u(t−td(t))

通过解析以下方程计算传输延迟:

此方程涉及到一个瞬时时滞 ti(t),由时滞(底部或右侧)输入指定:

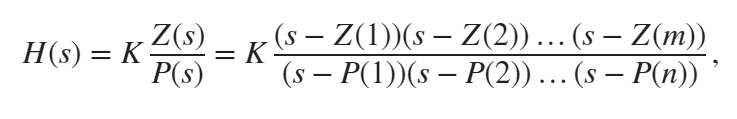

Zero-Pole

Zero-Pole 模块可以使用零点、极点和拉普拉斯域传递函数增益定义的系统进行建模。此模块可为单输入单输出 (SISO) 和单输入多输出 (SIMO) 系统建模。

传递函数

其中 Z 表示零点,P 表示极点,K 表示传递函数增益。

- 极点数必须大于或等于零点数。

- 如果极点和零点为复数,它们必须是复共轭对组。

- 对于多输出系统,所有传递函数必须具有相同的极点。零点的值可以不同,但每个传递函数的零点数必须相同。

Discontinuities模块

Backlash

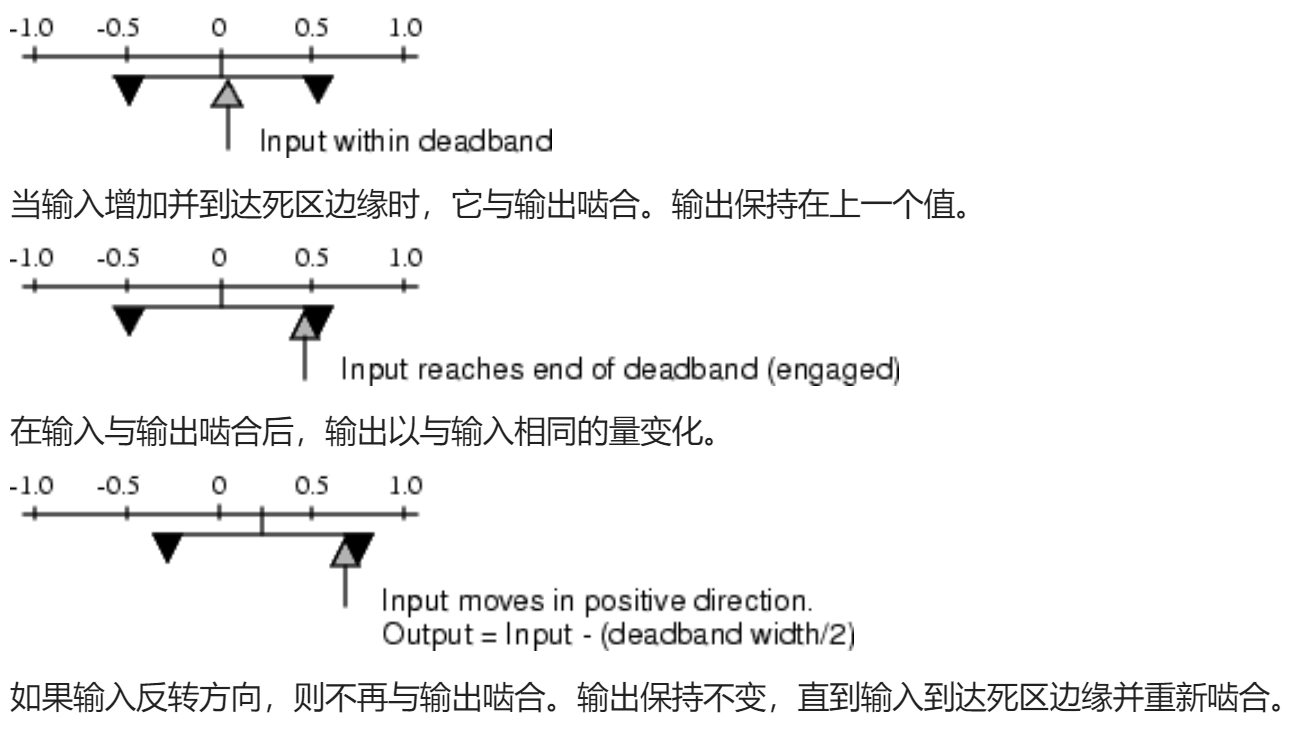

Backlash 模块实现这样一个系统,其中输入信号的改变使得输出信号产生相同的改变量,输入改变方向时除外。当输入信号方向改变时,输入信号的初始变化不会影响输出。系统的侧隙称为死区。死区位于输出信号的中心。下图显示了初始状态,默认死区宽度为 1,初始输出为 0。

Coulomb and Viscous Friction

Coulomb and Viscous Friction 模块用于对库仑(静态)摩擦和粘性(动态)摩擦进行建模。此模块可以对值为零时的不连续性以及非零时的线性增益进行建模。

y = sign(x) .* (Gain .* abs(x) + Offset)

其中 y 是输出,x 是输入,Gain 是非零输入值的信号增益,Offset 是库仑摩擦。此模块接受一个输入并生成一个输出。输入可以是标量、向量或包含实数和复数元素的矩阵。

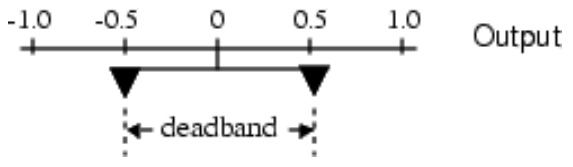

Dead Zone

在指定的区域(死区)内生成零值输出。死区下限:LL;死区上限:UL

| 输入 | 输出 |

|---|---|

| U >= LL 和 U <= UL | 零 |

| U > UL | U – UL |

| U < LL | U – LL |

Dead Zone Dynamic

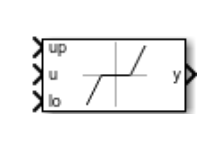

死区上限up和死区下限lo可变(动态变化)

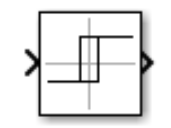

Hit Crossing

检测输入何时在由穿越方向属性指定的方向上到达穿越偏移量参数值。 输出为1或0。

输出为1或0。

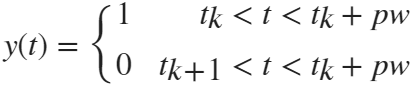

PWM

生成与输入占空比相对应的理想脉宽调制信号。

脉宽调制(PWM)是一种使用方脉冲对模拟信号进行编码的技术。这种编码是通过控制被设置为高的方波的一个周期的分数来实现的。这个分数是信号的占空比。调制信号和输入占空比之间的关系可以简单地描述为:

y = D y m a x + ( 1 − D ) y m i n y=Dy_{max}+(1-D)y_{min} y=Dymax+(1−D)ymin

PWM块的占空比限制在[0,1]

- 输入:D

- 输出:由输入占空比决定的PWM信号

Quantizer

按照给定间隔将输入离散化

Quantizer 模块使用量化算法离散化输入信号。该模块使用舍入到最接近整数方法将信号值映射到由量化区间定义的输出端的量化值。平滑的输入信号在量化后可能会呈现阶梯形状。

舍入到最接近整数方法:

y = q ⋅ round ( u q ) y=q\cdot\text{round}(\frac{u}{q}) y=q⋅round(qu)

- y:量化输出

- u:输入

- q:量化区间

Quantizer输出的量化级别是量化区间的整数倍,默认值为0.5。

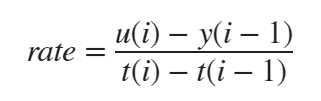

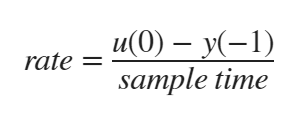

Rate Limiter

限制通过它的信号的一阶导数。输出的变化速率不大于指定的限制,导数的计算公式为:

其中 u ( i ) u(i) u(i)和 t ( i ) t(i) t(i)是当前第i步的模块的输入和时间。通过将rate与上升沿速率和下降沿速率参数进行比较来决定输出:

- 如果 rate 大于上升沿压摆率参数 (R),则输出的计算公式为_y_(i)=Δ_t_⋅_R_+y(_i_−1).

- 如果 rate 小于下降沿压摆率参数 (F),则输出的计算公式为_y_(i)=Δ_t_⋅_F_+y(_i_−1).

- 如果 rate 介于 R 和 F 之间,则输出的变化等于输入的变化:y(i)=u(i)

当模块在连续模式下运行时(例如,采样时间模式为“继承”,驱动模块的采样时间为零),将会忽略初始条件。t = 0 时的模块输出等于初始输入:

y ( 0 ) = u ( 0 ) y(0)=u(0) y(0)=u(0)

当模块在离散模式下运行时(例如,采样时间模式为“继承”,驱动模块的采样时间不为零),将会保留初始条件:

y ( − 1 ) = I c y(-1)=I_c y(−1)=Ic

其中 I c I_c Ic是初始条件。t=0时模块输出按照假设rate超出R和F的界限来计算。当t=0时,rate的计算公式为:

Relay

在两个常量输出之间切换

Relay 模块的输出在两个指定值之间切换。打开中继时,它会一直保持打开,直到输入低于关闭点参数的值为止。关闭中继时,它会一直保持关闭,直到输入高于开启点参数的值为止。此模块接受一个输入并生成一个输出。

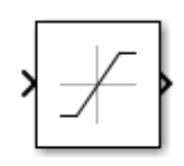

Saturation

将信号限制在饱和上界和饱和下界之间

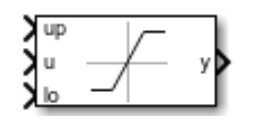

Saturation Dynamic

| 输入 | 输出 |

|---|---|

| lo ≤ 输入值 ≤ up | 输入值 |

| 输入值 < lo | 下限 |

| 输入值 > up | 上限 |

Variable Pulse Generator

输出描述:

- D:占空比

- P:输出信号的连续上升沿之间的时间,较小的值表示较高的频率。

Wrap to Zero

如果输入大于阈值,则将输出设置为零。当输入小于等于阈值时,输出等于输入。

Discrete模块

Delay

Delay模块按照设定的延迟后输出模块的输入。延迟时间由延迟长度所决定。在仿真的前几个时间步的输出取决于模块的采样时间、延迟长度和仿真开始时间。此模块支持指定或继承离散采样时间,以确定采样之间的时间间隔。

| 仿真时间范围 | 模块输出 |

|---|---|

| (Tstart) 到 (Tstart + Toffset) | 零 |

| (Tstart + Toffset) 到 (Tstart + Toffset + n * Tsampling) | 初始条件参数 |

| 在 (Tstart + Toffset + n * Tsampling) 之后 | 输入信号 |

Difference

计算一个时间步内的信号变化。输出当前输入值减去上一步的输入值的差值。

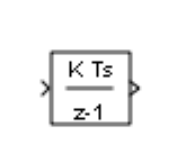

Discrete Derivative

计算可缩放性的离散导数:

y ( t n ) = K ( u ( t n ) − u ( t n − 1 ) T s ) y(t_n)=K(\frac{u(t_n)-u(t_{n-1})}{T_s}) y(tn)=K(Tsu(tn)−u(tn−1))

离散步长 T s T_s Ts必须是固定值。K为增益因子。

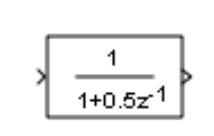

Discrete Filter

使用指定的数字IIR滤波器单独对输入信号的每个通道进行滤波。可以将滤波器结构指定为 Direct form I、Direct form I transposed、Direct form II 或 Direct form II transposed。该模块实现了具有固定系数的静态滤波器。可以调整这些静态滤波器的系数。

此模块随时间的推移单独对输入信号的每个通道进行滤波。输入处理参数用于指定该模块如何处理输入的每个元素。您可以指定将输入元素作为独立通道处理(基于采样的处理),或将输入的每个列作为独立通道处理(基于帧的处理)。

Discrete-Time Integrator

对于第一个时间步,模块状态为n=0,具有初始输出y(0)=IC或初始状态x0=IC,具体取决于初始条件设置的参数值。

对于仿真时间为t(n)的给定步长n>0,更新输出为:

- 前向欧拉方法:

y(n) = y(n-1) + K*[t(n) - t(n-1)]*u(n-1)

- 后向欧拉方法:

y(n) = y(n-1) + K*[t(n) - t(n-1)]*u(n)

- 梯形法:

y(n) = y(n-1) + K*[t(n)-t(n-1)]*[u(n)+u(n-1)]/2

Simulink 根据模块的采样时间(可以是显式或触发的采样时间)自动选择这些输出方程的状态空间实现。当使用显式采样时间时,对于所有 n > 0 的步长,t(n)-t(n-1) 将减小到采样时间 T。

Memory

输出上一个时间步的输入

Tapped Delay

- 输入:输入信号

- 输出:延迟的输入信号的所有版本。使用输出向量排序参数指定输出向量中延迟信号的排序。

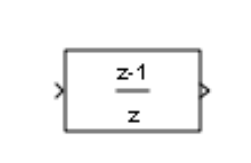

Unit Delay

Unit Delay 模块按指定的采样周期保持和延迟输入。当放置于迭代子系统中时,该模块将其输入保持并延迟一个迭代。此模块相当于 z − 1 z^{-1} z−1离散时间运算符。此模块接受一个输入并生成一个输出。每个信号可以是标量,也可以是向量。如果输入为向量,模块会按相同的采样周期保持和延迟向量中的所有元素。

| 模块 | 模块的用途 | 引用示例 |

|---|---|---|

| Unit Delay | 使用您指定的离散采样时间实现延迟。该模块接受并输出具有离散采样时间的信号。 | - Engine Timing Model with Closed Loop Control(Compression 子系统) |

| Memory | 将信号延迟一个主积分时间步。在理想情况下,该模块接受连续(或在子时间步中固定)的信号并输出在子时间步中固定的信号。 | - Building a Clutch Lock-Up Model(Friction Mode Logic/Lockup FSM 子系统) - Capture the Velocity of a Bouncing Ball with the Memory Block |

| Zero-Order Hold | 将具有连续采样时间的输入信号转换为具有离散采样时间的输出信号。 | - Developing the Apollo Lunar Module Digital Autopilot - 使用 MATLAB Function 模块的雷达跟踪 |

- 输出:延迟了一个采样周期的输入信号。

Logic and Bit Operations模块

Bit Clear

- 输入:存储的整数的指定位

- 输出:由设置为零的指定位组成。

- 位索引参数:位0是最低有效位。

Bit Set

- 输入:具有存储整数的指定位的输入信号

- 输出:指定位信号设置为1

Bit to Integer Converter

将输入向量中的比特组映射到输出向量中的整数。

- 如果M是由每整数位数(M)参数指定的,对于无符号整数,块将每组M位映射到范围为[0, 2M-1]的整数。其结果,输出向量长度是输入向量长度的1/M倍。

- 对于有符号整数,块将每组M位映射到范围为[-2M-1,2M-1-1]。

- 输入:指定为位的标量或列向量。其长度是每整数位数(M)参数中指定值的倍数。输入必须是0或1的位。

- 输出:以整数或整数列向量形式返回。位packing后,将结果整数值视为参数指定输入位是被视为无符号还是被视为有符号。

当输入位被视为无符号时,每个整数输出都在[0,(2M–1)]范围内。

当输入位被视为有符号时,每个整数输出都在[(–2M-1),(2M–1–1)]范围内。

Bitwise Operator

对输入执行指定的按位运算

为一个或多个操作数指定的按位运算。按位运算将操作数视为位向量,而不是单个值。Bitwise Operator 模块不支持移位运算。对于移位运算,请使用 Shift Arithmetic 模块。当配置为多输入 XOR 门时,此模块将按照 IEEE 逻辑元素标准的规定执行模 2 加法。

- 输入:

- 对于单个向量输入,模块会将运算(除 NOT 运算符外)应用于向量的所有元素。

- 对于两个或更多输入,模块将在所有输入之间执行运算。如果输入为向量,模块将在对应的向量元素之间执行运算以生成向量输出。

- 输出:指定为输出数据类型的输出信号,模块从驱动模块继承该输出数据类型,且该数据类型必须准确表示零。满足此条件的数据类型包括有符号整数和无符号整数数据类型。

模块输出的大小取决于输入的数量、向量大小以及您选择的运算符。如果您不指定位掩码,则输出为标量。如果您指定位掩码,则输出为向量。

按位逻辑运算符

AND(默认)| OR | NOR | NAND | XOR | NOT

Combinatorial Logic 模块实现一个标准真值表,用于建模可编程逻辑数组 (PLA)、逻辑电路、决策表和其他布尔表达式。此模块与 Memory 模块一起使用,以实现有限状态机或触发器。

Compare To Constant

Compare To Constant 模块用于将输入信号与常量进行比较。在常量值参数中指定常量。使用运算符参数指定输入与常量值的比较方式。

- 输出:若比较结果为false则输出0;若比较结果为true则输出1

Detect Fall Negative

当信号值降至严格负值,且其先前值为非负时,检测下降沿。

Detect Fall Negative块确定输入是否小于零,以及其先前值是否大于或等于零。

此块仅支持离散采样时间。

- 输出:

当输入信号小于零时为真(等于1),并且其先前值大于或等于零;当输入信号大于或等于零时为false(等于0),或者如果输入信号为负值,则其先前值也是负值。

Detect Change

Detect Change 模块确定输入信号是否不等于其上一个值。初始条件确定上一个输入 U/z 的初始值。

此模块仅支持离散采样时间。

- 输出:

当输入信号不等于上一个值时,为 true(等于 1);当输入信号等于上一个值时,为 false(等于 0)。

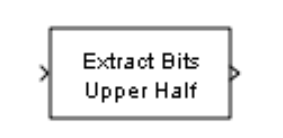

Extract Bits

Extract Bits 模块允许您从输入信号的存储整数值中输出选择的连续位。使用提取位参数定义选择输出位的方法。

- 选择 Upper half 输出一半的输入位,其中包含最高有效位。如果输入信号中有奇数数量的位,则按以下方程计算输出位数number of output bits = ceil(number of input bits/2)

- 选择 Lower half 输出一半的输入位,其中包含最低有效位。如果输入信号中有奇数数量的位,则按以下方程计算输出位数number of output bits = ceil(number of input bits/2)

- 选择 Range starting with most significant bit 以输出一定数量的输入信号最高有效位。在位数参数中指定要输出的最高有效位数。

- 选择 Range ending with least significant bit 以输出一定数量的输入信号最低有效位。在位数参数中指定要输出的最低有效位数。

- 选择 Range of bits 以在位索引参数中指定要输出的输入信号的一系列连续位。需要以 [start end] 格式指明范围,而输入位的索引将从 0(最低有效位)开始连续标记。

Integer To Bit Converter

Integer to Bit Converter块将输入矢量中的每个整数(或定点值)映射到输出矢量中的一组位。

此块为单速率和单通道。块将每个整数值(或使用定点输入时存储的整数)映射到一组M位,使用输出位顺序的选择来确定最高有效位。结果输出矢量长度是输入矢量长度的M倍。

Interval Test

如果输入介于下限和上限指定的值之间,Interval Test 模块将输出 true (1)。如果输入在这些值的范围之外,模块将输出 false (0)。当输入等于下限或上限时,模块的输出取决于选中左半闭区间还是右半闭区间复选框。

Logical Operator

Logical Operator 模块对其输入执行指定的逻辑运算。输入值为非零值时为 true (1),为零时则为 false (0)。

| 运算 | 描述 |

|---|---|

| AND | 如果所有输入均为 TRUE,则为 TRUE |

| OR | 如果至少有一个输入为 TRUE,则为 TRUE |

| NAND | 如果至少有一个输入为 FALSE,则为 TRUE |

| NOR | 如果所有输入均不为 TRUE,则为 TRUE |

| XOR | 如果有奇数个输入为 TRUE,则为 TRUE |

| NXOR | 如果有偶数个输入为 TRUE,则为 TRUE |

| NOT | 如果输入为 FALSE,则为 TRUE |

如果选择“不同”作为图标形状,则模块的外观会指示其功能。Simulink® 软件将按照 IEEE® 逻辑函数的图形符号标准,显示所选运算符的独特形状。

要指定输入端口的数量,请使用输入端口数目参数。使用输出数据类型参数指定输出类型。如果为 TRUE,则输出值为 1,如果为 FALSE,则输出值为 0。

Relational Operator

Relational Operator 模块对输入执行指定的关系运算。为关系运算符参数选择的值确定模块是接受一个还是两个输入信号。

Math Operations