FPGA时钟资源详解(4)——区域时钟资源

FPGA时钟系列文章总览:

FPGA原理与结构(14)——时钟资源![]() https://ztzhang.blog.csdn.net/article/details/132307564

https://ztzhang.blog.csdn.net/article/details/132307564

目录

一、概述

二、Clock-Capable I/O

三、I/O 时钟缓冲器 —— BUFIO

3.1 I/O 时钟缓冲器

3.2 BUFIO原语

四、区域时钟缓冲器——BUFR

4.1 区域时钟缓冲器

4.2 BUFR原语

五、区域时钟网

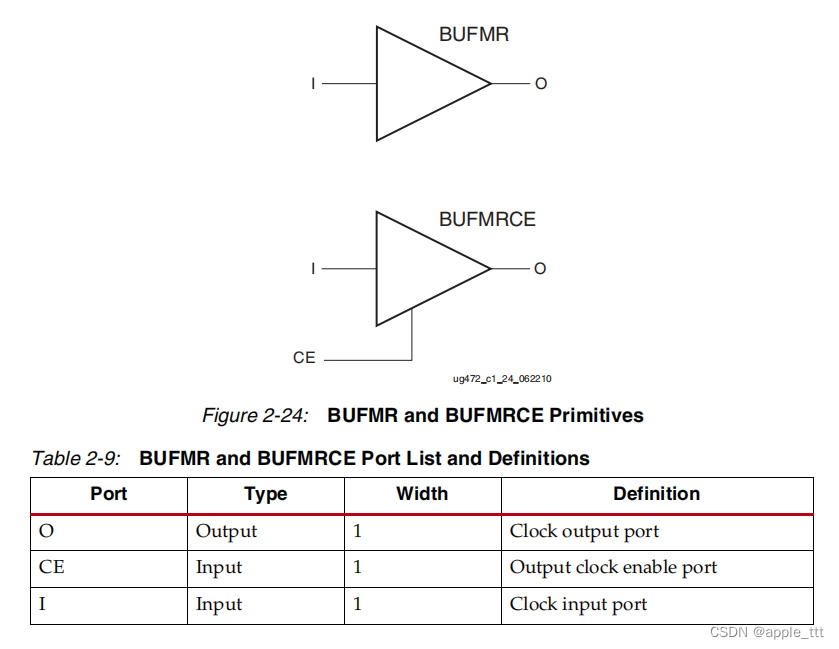

六、多区域时钟缓冲器——BUFMR/BUFMRCE

6.1 多区域时钟缓冲器

6.2 BUFMR/BUFMRCE原语

七、水平时钟缓冲器—— BUFH, BUFHCE

7.1 水平时钟缓冲器

7.2 BUFH, BUFHCE原语

一、概述

区域时钟网络(Regional Clock Networks)在 Xilinx 7系列 FPGA 设计中提供了与全局时钟网络(Global Clock Network)相独立的时钟分配机制。这种区域性的时钟网络通过 BUFR(区域时钟缓冲器)实现,与全局时钟缓冲器(如 BUFG)相比,BUFR 提供的时钟信号范围限定在单个时钟区域内,且一个I/O时钟信号仅驱动单个bank。这种设计使得区域时钟网络特别适用于源同步接口设计。

二、Clock-Capable I/O

在FPGA设计中的每个时钟区域,每个 I/O 组在每个 I/O 列中都有四对具备时钟能力(Clock-Capable)的 I/O 引脚对。这些具备时钟能力的 I/O 引脚对是位于特定位置的专用 I/O 对,它们与附近的区域时钟资源和其他时钟资源有特殊的硬件连接。此外,这些具备时钟能力的 I/O 对还可以作为常规的 I/O 对使用。每个bank都有四个专用的具备时钟能力的 I/O site。当作为时钟输入使用时,具备时钟能力的引脚可以驱动 BUFIO、BUFMR 和 BUFR。每个 I/O 列支持区域时钟缓冲器(BUFR)。每个设备有两个 I/O 列。

一个 CCIO(Clock-Capable I/O)可以驱动同一区域内的任何 BUFR,但只有专用的 CC(具备时钟能力的引脚)可以以 1:1 的关系驱动特定的 BUFIO,而 MRCC(多区域时钟控制器)可以驱动 BUFMR。这意味着 CCIO 到特定 BUFIO 或 BUFMR 的连接只有一个。这些连接和资源分配机制为 FPGA 设计提供了高度的灵活性和精确的时钟管理能力,有助于实现高效和稳定的系统设计。

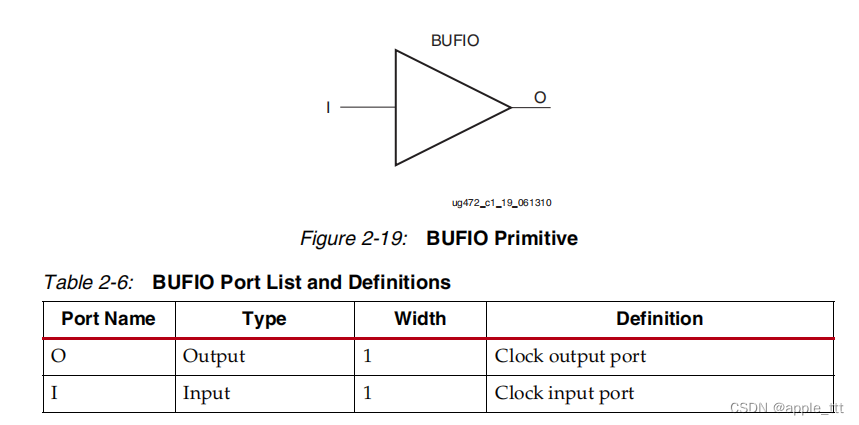

三、I/O 时钟缓冲器 —— BUFIO

3.1 I/O 时钟缓冲器

I/O 时钟缓冲器(BUFIO)是 7 系列设备中提供的一种时钟缓冲器。BUFIO 在 I/O 组内驱动一个专用的时钟网络,这个网络独立于全局时钟资源。因此,BUFIO 特别适合于源同步数据捕获(前向/接收器时钟分配)。BUFIO 由位于同一bank的具备时钟能力的 I/O、来自 MMCM 的高性能时钟(HPC),或者位于同一及相邻区域的 BUFMR 驱动。在一个时钟区域内,每个bank有四个 BUFIO。每个 BUFIO 可以在同一区域/bank内驱动单个 I/O 时钟网络。BUFIO 不能驱动逻辑资源(如 CLB、块 RAM、DSP 等),因为 I/O 时钟网络仅覆盖同一bank/时钟区域内的 I/O 列。

3.2 BUFIO原语

BUFIO是一个时钟输入,时钟输出缓冲区。在输入和输出之间存在一个相位延迟。

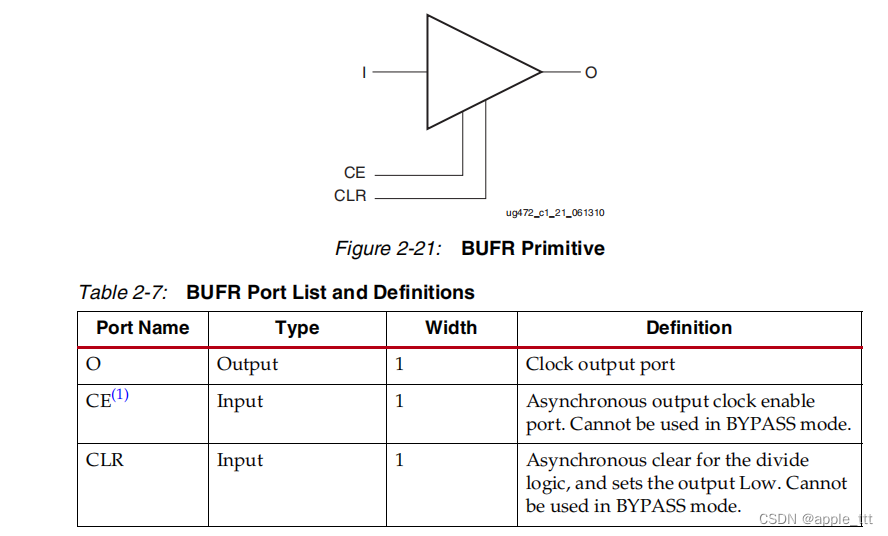

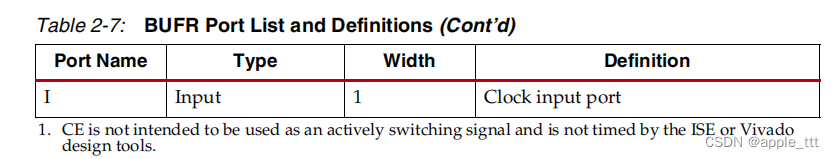

四、区域时钟缓冲器——BUFR

4.1 区域时钟缓冲器

区域时钟缓冲器(BUFR)是 7 系列设备中提供的另一种时钟缓冲器,它能够独立于全局时钟树,将时钟信号驱动到位于同一时钟区域内的专用时钟网络。每个 BUFR 能够驱动它所在区域内的4个区域时钟网络。与 BUFIOs 不同,BUFRs 既可以驱动 I/O 逻辑,也可以驱动逻辑资源(如 CLB、块 RAM 等)。BUFRs 可以由具备时钟能力的引脚、局部互连、MMCMs 的高性能时钟输出(CLKOUT0 至 CLKOUT3)或同一及相邻区域内的 BUFMRs 驱动。此外,BUFRs 还能够生成相对于时钟输入的分频时钟输出,分频值是一个介于 1 到 8 的整数。对于需要时钟域交叉或串转并转换的源同步应用而言,BUFRs 是理想的选择。

每个 I/O 列都支持区域时钟缓冲器。每个设备有两个 I/O 列。BUFRs 也可以直接驱动 MMCM 的时钟输入和 BUFGs。

4.2 BUFR原语

BUFR是一个时钟输入/时钟输出缓冲器,能够划分输入时钟频率。7系列FPGAs缓冲器也可以直接驱动MMCM时钟输入和缓冲器。

五、区域时钟网

7系列 FPGA 设备除了包含全局时钟树和网络外,还包含区域时钟树和网络。区域时钟树同样设计用于低偏斜和低功耗运作,未使用的分支会被断开。区域时钟树还负责管理负载/扇出,尤其是当所有逻辑资源被使用时。

区域时钟网络不会贯穿整个 7 系列设备,而是仅限于单个时钟区域。一个时钟区域包含四个独立的区域时钟网络。要访问区域时钟网络,必须实例化 BUFRs。

为了利用区域时钟网络的优势,设计师需要在设计中实例化 BUFR。通过 BUFR,可以将时钟信号精确地分配给同一时钟区域内的逻辑资源,支持复杂时钟管理需求。实例化 BUFR 时,设计师可以根据具体的设计需求选择合适的分频比例,以及决定是否启用其他高级功能,如时钟门控。

六、多区域时钟缓冲器——BUFMR/BUFMRCE

6.1 多区域时钟缓冲器

BUFMR 是一种在 7 系列 FPGA 设备中用于支持跨多个区域/bank的时钟缓冲器,它取代了在先前 Virtex 架构中可用的 BUFR 和 BUFIO 的多区域/bank支持功能。每个bank内设有两个 BUFMR,每个缓冲器可以由同一bank内的一个特定的多区域时钟控制器(MRCC)驱动。MRCC 引脚在引脚名中标有 MRCC(例如:IO_L12P_T1_MRCC_12 或 IO_L12N_T1_MRCC_12),表示这些引脚为多区域时钟控制器引脚,包括 P 引脚和 N 引脚。BUFMR 可以驱动同一区域/bank内的 BUFIO 和/或 BUFR,以及上方和下方区域/bank内的 BUFIO 和 BUFR。

6.2 BUFMR/BUFMRCE原语

BUFMR(多区域时钟缓冲器)是一种具有时钟使能(CE)功能的时钟输入/输出缓冲器。取消使能 CE 会停止输出时钟。BUFMR 被设计用来驱动 BUFR(区域时钟缓冲器)和 BUFIO(I/O时钟缓冲器),以便将时钟信号路由到同一区域/银行及相邻的区域/bank。BUFMR 可以由同一区域内的多区域时钟控制器(MRCC)或是 GT(吉比特收发器)时钟驱动。

要将 BUFMR 或 BUFMRCE 与 BUFIOs 结合使用,接口引脚必须位于三个bank之内。同样地,如果要与 BUFRs 结合使用,逻辑必须位于最多三个区域(region)内(如果使用了三个 BUFRs)。如果在与 BUFRs/BUFIOs 所在的同一bank或区域中放置了存储器接口,那么从 BUFMR 到该bank或区域中的 BUFHs/BUFIOs 的连通性可能会受到限制。

BUFMRCE 的拓扑结构显示了如何将 BUFMRCE 与相邻的 BUFIOs 或 BUFRs 连接,以及它们如何分布在 FPGA 设计中。BUFMRCE 提供了一种高效的方式来管理跨多个bank或区域的时钟信号,但它的使用需要仔细考虑银行或区域内的资源分配和布局,以确保时钟信号的有效传输和最小化布局限制。

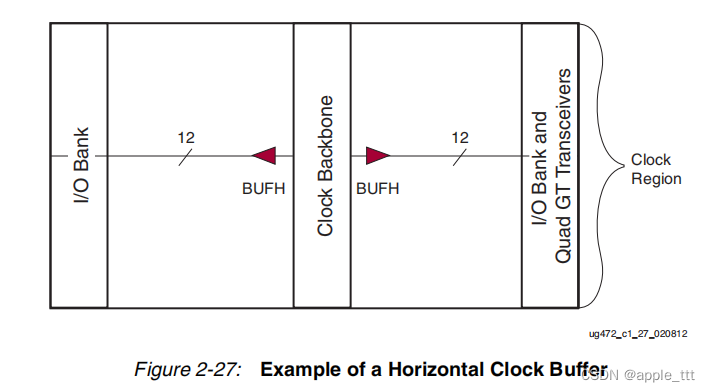

七、水平时钟缓冲器—— BUFH, BUFHCE

7.1 水平时钟缓冲器

水平时钟缓冲器(BUFH)在单个区域内驱动一个水平的全局时钟树主干。每个区域有 12 个 BUFH 可供使用。每个 BUFH 都有一个时钟使能引脚(CE),允许动态地关闭时钟。BUFH 可以由以下来源驱动:

- 同一区域内的 MMCM/PLL 输出

- BUFG 输出

- 同一或水平相邻时钟区域的 GT 输出时钟

- 局部互连

- 来自同一水平相邻区域/银行的左侧或右侧 I/O 银行的具备时钟能力的输入

BUFH 提供了一种有效的方式来扩展时钟信号的覆盖范围,尤其适合于需要在 FPGA 设计的特定区域内分配时钟信号的情况。通过使用 BUFH,设计师可以实现对时钟信号的精确控制,包括根据需要动态启用或禁用时钟,从而优化系统性能和功耗。

7.2 BUFH, BUFHCE原语

要使用 BUFH,逻辑必须适应水平相邻的两个区域(左和右)。时钟使能引脚可以完全关闭时钟,从而实现潜在的功耗节省。与 BUFG 驱动两个相邻区域相比,BUFH 的功耗和抖动更低。

这表明 BUFH 特别适用于需要跨越水平相邻区域分配时钟信号的设计,同时对功耗和时钟信号质量有较高要求的场景。利用 BUFH 的时钟使能功能,设计师可以根据系统的实际需求动态管理时钟信号,不仅优化了系统的性能,还有效降低了功耗。