vivado ILA 交叉触发

ILA 交叉触发

ILA 交叉触发功能支持在 ILA 核之间以及在 ILA 核与处理器 ( 如 Zynq ® -7000 SoC ) 之间进行交叉触发。如需在位于不

同时钟域中的 2 个 ILA 核之间执行触发 , 或者要在处理器与 ILA 核之间执行硬件 / 软件交叉触发 , 可使用该功能。

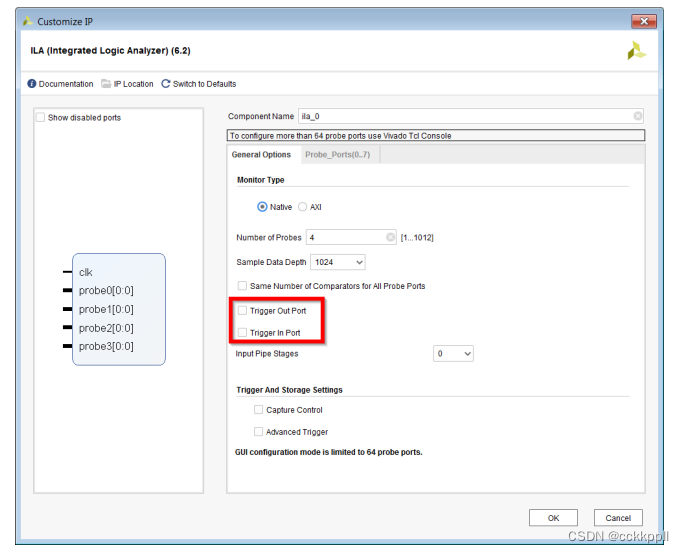

要使用交叉触发功能 , 在核生成时 , 应配置 ILA 核心以使其包含专用触发器输入端口 ( TRIG_IN 和 TRIG_IN_ACK ) 和

专用触发器输出端口 ( TRIG_OUT 和 TRIG_OUT_ACK ) 。如果要使用 ILA 触发器输入或输出信号 , 则必须使用将 ILA

核添加到设计中的 HDL 例化方法。

TRIG_OUT_ACK 是 ILA 核 ( 另一个 ILA 、用户设计或处理器 ) 的指示信号 , 表明已正确接收到 TRIG_OUT , 它会导致

ILA 在接收到 TRIG_OUT_ACK 时拉低 TRIG_OUT 信号。

换言之 , TRIG_OUT 将保持高电平直至 TRIG_OUT_ACK 可用为止。如果 TRIG_OUT_ACK 信号绑定到低电平 , 那么

TRIG_OUT 将保持高电平 , 直至用户重新装备 ILA 为止。届时 TRIG_OUT 才会转至低电平。如果 TRIG_OUT_ACK 绑

定到低电平 , 那么您可重新装备 ILA 。

以下显示了典型的交叉触发设置 , 其中 ILA2 交叉触发到 ILA1 内。 ILA2 的 TRIG_OUT 信号连接到 ILA1 的 TRIG_IN 信

号。 ILA1 的 TRIG_IN_ACK 信号则连接到 ILA2 的 TRIG_OUT_ACK 信号。

(ILA 2) trig_out -> (ILA 1) trig_in

(ILA 1) trig_in_ack -> (ILA 2) trig_out_ack

• 假定驱动 trig_in 端口的逻辑与 ILA clk 保持同步。

• 当 trig_in 断言有效后 , trig_in_ack 信号需经过 1 个时钟周期后才能断言有效。

• 当使用 trig_in 或者满足触发条件后 , trig_out 信号需经过 9 个时钟周期才能断言有效。

• 仅当触发器信号断言无效后 , trig_in_ack 和 trig_out_ack 信号才会转至低电平。

如需获取有关在 FPGA 互连结构与 Zynq-7000 SoC 处理器之间使用交叉触发功能的详细教程 , 请参阅《 Vivado Design

Suite 教程 : 嵌入式处理器硬件设计》 ( UG940 ) 。

例化调试核

生成调试核后 , 在 HDL 源代码中将其例化 , 然后将其连接到要探测的信号以便对其进行调试。以下是 Verilog HDL 源

文件中的 ILA 实例的示例 :

u_ila_0

(

.clk(clk),

.probe0(counterA),

.probe1(counterB),

.probe2(counterC),

.probe3(counterD),

.probe4(A_or_B),

.probe5(B_or_C),

.probe6(C_or_D),

.probe7(D_or_A)

);

注释 : 不同于旧的 VIO 和 ILA v1.x 核 , 新的 ILA 核实例无需连接至 ICON 核实例。而改为将 Debug Hub 核 ( dbg_hub )

自动插入已综合的设计网表 , 以便在新的 ILA 核与 JTAG 扫描链之间提供连接。

对包含调试核的设计执行综合

下一步 , 在 Vivado Design Suite 中单击“ Run Synthesis ”或者运行以下 Tcl 命令来对包含调试核的设计执行综合 :

launch_runs synth_1

wait_on_run synth_1

您也可以使用 synth_design Tcl 命令来对设计执行综合。如需了解有关各种设计综合方法的更多详细信息 , 请参阅

《 Vivado Design Suite 用户指南 : 综合》 ( UG901 ) 。

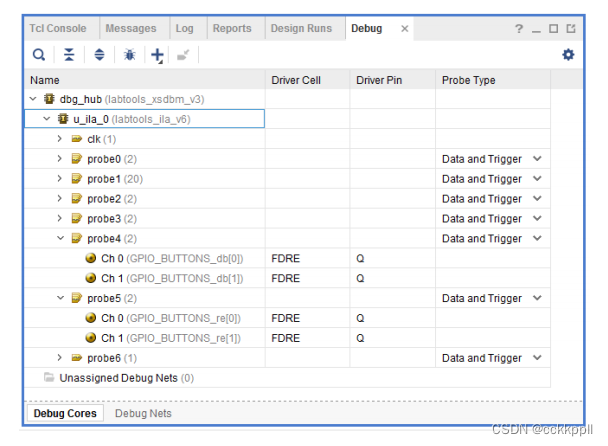

在已综合的设计内查看调试核

完成设计综合后 , 您可打开已综合的设计 , 以查看调试核并修改其属性。单击 Flow Navigator 中的“ Open

Synthesized Design ”以打开已综合的设计 , 然后选中“ Debug ”窗口布局以打开“ Debug ”窗口 , 其中会显示您的

ILA 调试核已连接到 Debug Hub 核 ( dbg_hub ) , 请参阅下图。

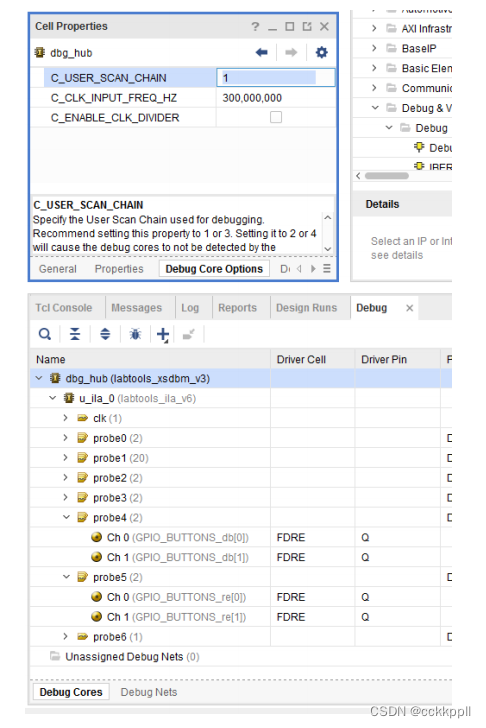

更改 Debug Hub 核的 BSCAN 用户扫描链

您可通过如下方式来查看和更改 Debug Hub 核的 BSCAN 用户扫描链索引 : 选择“ Debug ”窗口中的“ dbg_hub ”、

选择“ Properties ”窗口中的“ Debug Core Options ”视图 , 然后更改“ C_USER_SCAN_CHAIN ”属性的值 ( 请参阅下

图 ) 。

重要提示 ! 对于 Debug Hub 核 , C_USER_SCAN_CHAIN 默认值为 1 。如果对于 Debug Hub 核使用的扫描链值

不为 1 , 则必须在器件上通过硬件管理器来手动更改这些值。请参阅“硬件器件编程”以获取更多详细信息。

重要提示 ! 如果您计划使用 Microprocessor Debug Module (MDM) 或者其它将 BSCAN 原语与 Vivado 逻辑调试

核搭配使用的 IP , 那么您需要将 dbg_hub 的 C_USER_SCAN_CHAIN 属性设置为与其它 IP 扫描链设置不冲突

的用户扫描链。否则 , 可能导致后续实现流程中出错。