PCIe的链路状态

目录

概述

链路训练的目的

两个概念

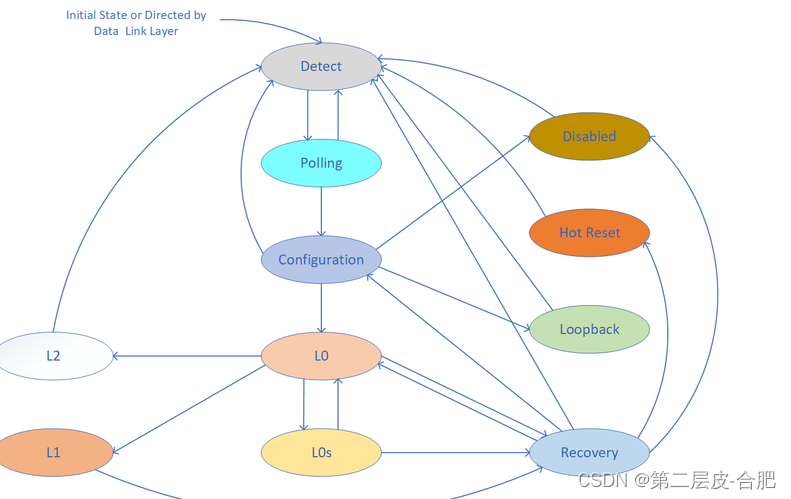

下面介绍LTSSM状态机

概述

PCie链路的初始化过程较为复杂,Pcie总线进行链路训练时,将初始化Pcie设备的物理层,发送接收模块和相关的链路状态信息,当链路训练成功结束后,PCIe链路两端的设备可以进行通讯。

链路训练主要由硬件逻辑完成,而无需系统软件的参与。此外当PCie设备从低功耗状态返回到正常工作模式时,或者PCie出现错误时,也需要进行重新连接。

链路训练的目的

主要是进行PCie物理层,端口配置信息,相应的链路状态,并了解链路对端的拓扑结构,以便PCie链路两端的设备进行通信。

Lane reveral :PCie链路两端的设备所使用的的lane可以错序进行连接

Polarity inversion:在单lane上,差分的极性也可以进行错序连接

以上功能就是为了方便PCB走线,因为差分信号要求在PCB中等长而且等距,在一个系统中,如果存在多个差分,PCB布线较为困难。

De-skew:PCI总线可以使用多个lane进行数据交换,而数据报文经过不同的lane的延时并不完全相同,PCie总线进行训练时,需要处理这些不通lane的延时差异,并进行补偿

在PCIe总线中,如果一个pcie链路的两端分别连接不通类型的PCie设备,将选择较低的数据速率,值得注意的是,在链路初始化时,首先使用2.5t之后,在切到更高的速率。

两个概念

Link numbei 与lane number。

在一个switch中存在多个下游,并使用0~n,进行编号,这些编号存在swith的硬件逻辑中,而不再配置空间中,整个编号也称为link number

Lane number 分为两类,一类时物理lane number(链路训练之前) 另一类是逻辑lane number(链路训练之后,)应为PCIE容许错序连接,因此,逻辑lane和物理lane并不一定相同,因此在总线链路训练时,需要对rc或者sw的link初始化。

Bit lock:pcie总线进行数据传输时,需要进行时钟同步,但是pcie链路并没有这个时钟信号,因此在进行总线训练时,接收端需要从发送端的数据报文中提取接受时钟,这个过程称为bit lock

Symbol lock:在链路训练中,PCIe链路需要首先确认COM字符。11000001010,00111110101

L链路训练特殊字符序列(PLP)

TS1和TS2:TS1主要检测PCie的链路配置信息,而ts2确认TS1序列的检测结果;

(仅仅时第6到15的字符含义不通)

0:COM控制字符,表示ts1和ts2序列的开始,字符序列将复位LF-SR序列。

1:在链路的初始化阶段,第一个字符放置pad,即为空;而在链路配置阶段,该字符放置端口的link number。

2:在链路训练阶段,第一个字符放置pad,即为空,而在链路配置阶段,该字符放置端口的lane number;

3:FTS的个数,不通的PCIe链路需要使用不通德FTS序列,才能使接收端的PLL锁定接受时钟。

4:存放当前PCie设备支持的数据速率。

5:存放命令,第一位为hot reset; 第二位式:loopback;第三位式:disable scrambling 第四位是:compliance receive。当接受逻辑收到TS1/TS2序列后,将根据该字符进行对应操作。

IDLE;在正常情况下,在发送端进入到electrical idle 状态,必须向对端进行eios序列。

FTS:单个FTS序列由一个com和三个FTS组成,该序列的主要目的是使接受逻辑重新获得bit/symbol lock;

Skip:

由一个com和三个skip、字符组成,主要目的是进行时钟补偿,PCIe的时钟2.5G+-300ppm,其中300ppm意味着。一百万个时钟,会出现300个偏移。如果PCIE不使用skip序列,本地时钟与从报文中提取存在飘逸,可能导致数据传输失败。

在PCIe设备接受逻辑中,使用了两个时钟,一个时钟是从PLL报文中恢复,一个是本地时钟。在总线中,使用elastic buffer 技术处理者这两个时钟之间的频率差和相位差,elastic buffer由一个buff组成,该FIFO的一端使用本地时钟域,另一端使用恢复的时钟域。由于时钟的不匹配,将出现overrun和underrun。总线规定在1190-1538字符之后,必须发送skip序列进行补偿。

下面介绍LTSSM状态机