4位先行进位电路 logisim_数字集成电路的自动化设计作业—1

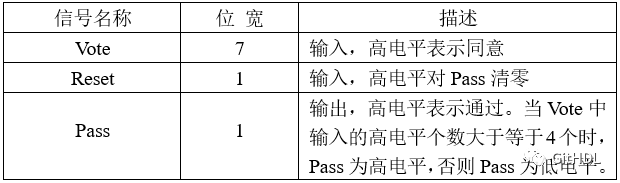

1、七人投票表决电路

Verilog代码如下:

module vote_7(

input [6:0] Vote,

input Reset,

output Pass);

integer i;

reg [2:0] vote_count;

always @(*) begin

if (Reset)

begin

vote_count = 3'd0;

end

else

begin

vote_count = 3'd0;

for (i=0;i<7;i=i+1)

begin

if (Vote[i] == 1) vote_count = vote_count + 1'd1;

end

end

end

assign Pass = (vote_count >= 3'd4) ? 1 : 0;

endmodule

测试代码如下:

//vote_7_tb

`timescale 1 ns/1 ns

module vote_7_tb();

reg [6:0] Vote;

reg Reset;

wire Pass;

vote_7 my_vote_7(

.Vote(Vote),

.Reset(Reset),

.Pass(Pass));

initial

begin

Vote=7'b0000001; Reset=0;

#5 Vote=7'b0000111; Reset=1;

#5 Vote=7'b0001111; Reset=0;

#5 Vote=7'b0011111; Reset=0;

#5 Vote=7'b0111111; Reset=0;

#5 Vote=7'b1111111; Reset=0;

#5 Vote=7'b1100111; Reset=0;

#5 Vote=7'b1100101; Reset=1;

#5 Vote=7'b1110101; Reset=0;

#5 $stop;

end

endmodule

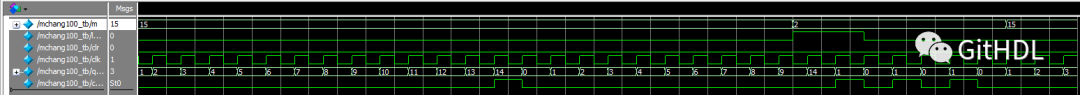

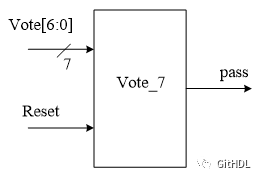

仿真波形如下(清晰显示请点开放大):

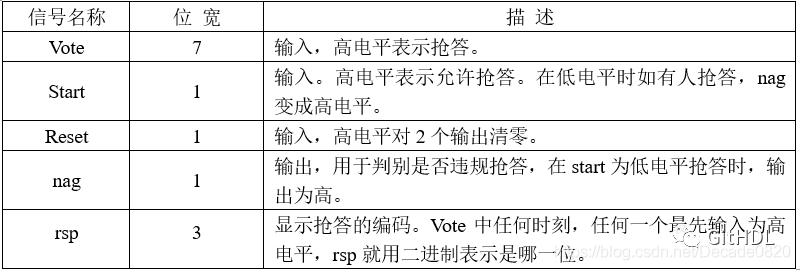

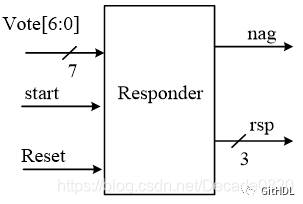

2、七人抢答电路

Verilog代码如下:

module responder(

input [6:0] vote,

input start,

input reset,

output reg nag,

output reg [2:0] rsp

);

always @(*) begin

if (reset)

begin

nag = 1'b0;

sp = 3'b0;

end

else if (start)

begin

case (vote)

7'b0000001: begin rsp = 3'b001; nag = 1'b0; end

7'b0000010: begin rsp = 3'b010; nag = 1'b0; end

7'b0000100: begin rsp = 3'b011; nag = 1'b0; end

7'b0001000: begin rsp = 3'b100; nag = 1'b0; end

7'b0010000: begin rsp = 3'b101; nag = 1'b0; end

7'b0100000: begin rsp = 3'b110; nag = 1'b0; end

7'b1000000: begin rsp = 3'b111; nag = 1'b0; end

default: begin rsp = 3'b000; nag = 1'b0; end

endcase

end

else if (vote)

nag = 1'b1;

end

endmodule

测试代码如下:

`timescale 1 ns/1 ns

module responder_tb();

reg [6:0] vote;

reg start;

reg reset;

wire nag;

wire [2:0] rsp;

responder my_responder(

.vote(vote),

.start(start),

.reset(reset),

.nag(nag),

.rsp(rsp)

);

initial

begin

reset=0; start=1; vote=7'b1000000;

#5 reset=1; start=1; vote=7'b1000000;

#5 reset=1; start=0; vote=7'b1000000;

#5 reset=0; start=0; vote=7'b1000000;

#5 reset=0; start=1; vote=7'b0000001;

#5 reset=0; start=1; vote=7'b0000010;

#5 reset=0; start=1; vote=7'b0000100;

#5 reset=0; start=1; vote=7'b0001000;

#5 reset=0; start=1; vote=7'b0010000;

#5 reset=0; start=1; vote=7'b0100000;

#5 reset=0; start=1; vote=7'b1000000;

#5 reset=0; start=1; vote=7'b1111001;

#10 $stop;

end

endmodule

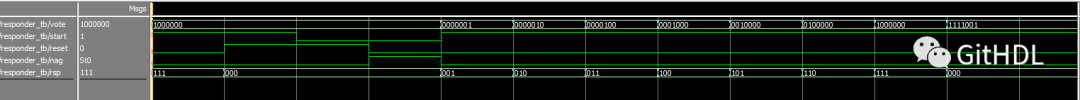

仿真波形如下(清晰显示请点开放大):

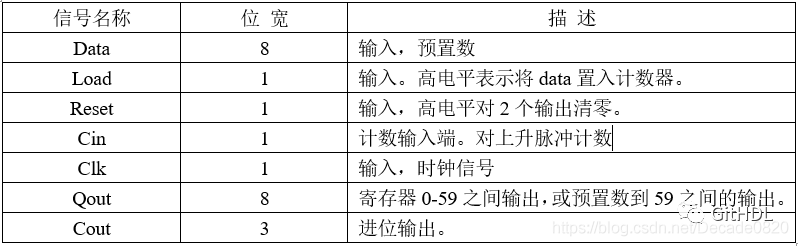

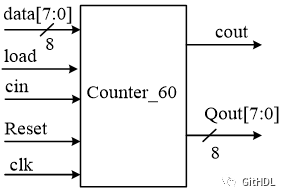

3、模为60的BCD码加法计数器

备注:这里将进位输出cout设置为1位,而不是题目给出的3位。

Verilog代码如下:

module counter_60(

input [7:0] data,

input load,

input reset,

input cin,

input clk,

output reg [7:0] qout,

output cout

);

always @(posedge clk)

begin

if (reset)

qout <= 0;

else if (load)

qout <= data;

else if (cin)

begin

if (qout[3:0] == 4'h9)//判断低位是否为9,是则

begin

qout[3:0] <= 0;//返回0

if (qout[7:4] == 4'h5)//并判断高位是否为5

qout[7:4] <= 0;

else

qout[7:4] <= qout[7:4] + 1'b1;//若高位不为5,则加1

end

else

qout[3:0] <= qout[3:0] + 1'b1;//若低位不为9,则加1

end

end

assign cout = ((qout == 8'h59) & cin) ? 1 : 0; //产生进位输出信号

endmodule

测试代码如下:

`timescale 1 ns/1 ns

module counter_60_tb();

reg [7:0] data;

reg reset, load, cin;

reg clk;

wire [7:0] qout;

wire cout;

counter_60 my_counter_60(

.data(data),

.reset(reset),

.load(load),

.cin(cin),

.clk(clk),

.qout(qout),

.cout(cout)

);

initial

begin

load=1'b0; reset=1'b0; data=8'h00; cin=1'b0;

#5 load=1'b0; reset=1'b1; data=8'h01; cin=1'b0;

#5 load=1'b0; reset=1'b0; data=8'h01; cin=1'b1;

#3 load=1'b1; reset=1'b0; data=8'h38; cin=1'b1;

#40 load=1'b0; reset=1'b0; data=8'h01; cin=1'b1;

#5 load=1'b0; reset=1'b0; data=8'h23; cin=1'b1;

#10 $stop;

end

initial

clk=0;

always

#2 clk = ~clk;

endmodule

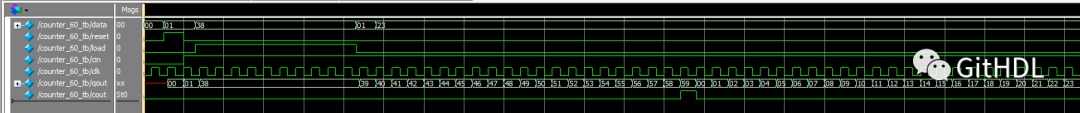

仿真波形如下(清晰显示请点开放大):

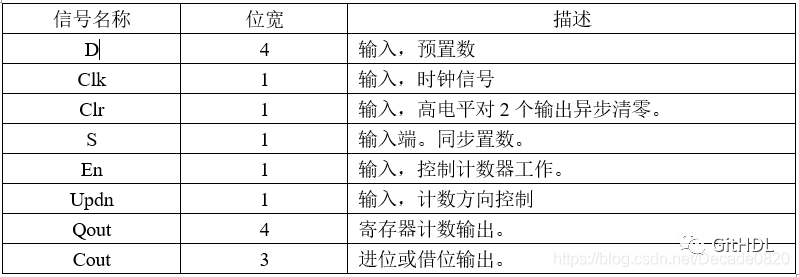

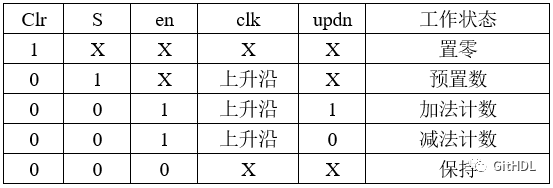

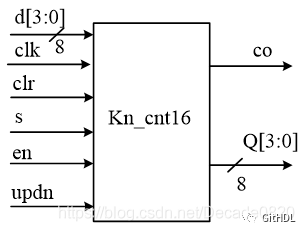

4、可逆计数器

备注:这里将进位输出cout设置为1位,而不是题目给出的3位。

Verilog代码如下:

module kn_cnt16(

input [3:0] data,

input clk,

input clr,

input set,

input en,

input updn,

output reg [3:0] qout,

output reg cout);

always @(posedge clk or posedge clr)

begin

if (clr) begin qout <= 0; cout <= 0; end

else if (set) begin qout <= data; cout <= 0; end

else if (en)

begin

case (updn)

1: begin

if (qout[3:0] == 4'b1111)

begin

qout[3:0] <= 4'b0000;

cout <= 1'b1;

end

else

begin

qout[3:0] <= qout[3:0] + 1'b1;

cout <= 1'b0;

end

end

0: begin

if (qout[3:0] == 4'b0000)

begin

qout[3:0] <= 4'b1111;

cout <= 1'b1;

end

else

begin

qout[3:0] <= qout[3:0] - 1'b1;

cout <= 1'b0;

end

end

endcase

end

end

endmodule

测试代码如下:

//kn_cnt16_tb

module kn_cnt16_tb();

reg [3:0] data;

reg clk;

reg clr, set, en, updn;

wire [3:0] qout;

wire cout;

kn_cnt16 my_kn_cnt16(

.data(data),

.clk(clk),

.clr(clr),

.set(set),

.en(en),

.updn(updn),

.qout(qout),

.cout(cout)

);

initial

begin

clk=1'b0; clr=1'b0; set=1'b0; en=1'b0; updn=1'b0; data=4'b0001;

#5 clr=1'b0; set=1'b1; en=1'b0; updn=1'b0; data=4'b0010;

#5 clr=1'b0; set=1'b0; en=1'b0; updn=1'b0; data=4'b0010;

#5 clr=1'b0; set=1'b0; en=1'b1; updn=1'b1; data=4'b0010;

#60 clr=1'b1; set=1'b0; en=1'b1; updn=1'b0; data=4'b0010;

#5 clr=1'b0; set=1'b0; en=1'b1; updn=1'b0; data=4'b1110;

#60 clr=1'b1; set=1'b0; en=1'b1; updn=1'b0; data=4'b0010;

#5 $stop;

end

always #2 clk = ~clk;

endmodule

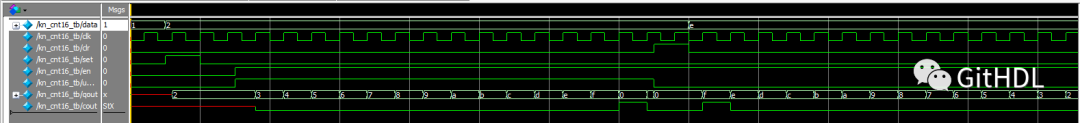

仿真波形如下(清晰显示请点开放大):

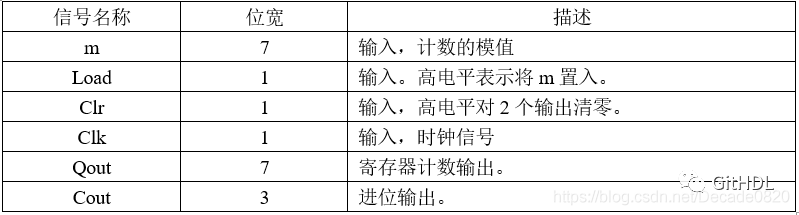

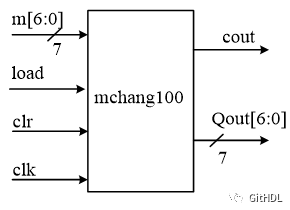

5、可变模计数器

备注:这里将进位输出cout设置为1位,而不是题目给出的3位。

Verilog代码如下:

module mchang100(

input [6:0] m,

input load,

input clr,

input clk,

output reg [6:0] qout,

output cout);

reg [6:0] md;

always @(posedge clk) begin

md <= m - 1'd1;

if (clr)

begin

qout[6:0] <= 6'd0;

end

else

begin

if (load)

begin

qout[6:0] <= md;

end

else

begin

if (qout[6:0] == md)

begin

qout[6:0] <= 6'd0;

end

else

begin

qout[6:0] <= qout[6:0] + 1'd1;

end

end

end

end

assign cout = (qout[6:0] == md) ? 1 : 0;

endmodule

测试代码如下:

// mchang100_tb

`timescale 1 ns/1 ns

module mchang100_tb();

reg [6:0] m;

reg load, clr;

reg clk;

wire [6:0] qout;

wire cout;

mchang100 my_mchang100(

.m(m),

.load(load),

.clr(clr),

.clk(clk),

.qout(qout),

.cout(cout)

);

initial

begin

clk=1'b0; m=7'b0001111; clr=1'b1; load=1'b0;

#5 m=7'b0001111; clr=1'b0; load=1'b1;

#5 m=7'b0001111; clr=1'b0; load=1'b0;

#50 m=7'b0000010; clr=1'b0; load=1'b1;

#5 m=7'b0000010; clr=1'b0; load=1'b0;

#10 m=7'b0001111; clr=1'b0; load=1'b0;

#5 $stop;

end

always

#1 clk = ~clk;

endmodule

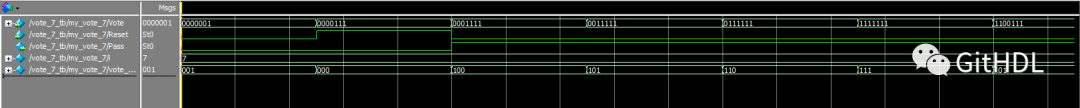

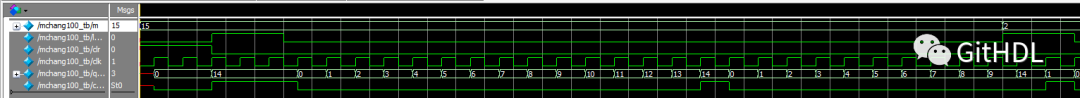

仿真波形如下(清晰显示请点开放大):

下图是15进制

下图是2进制