【操作系统】第五章 IO

第五章 IO系统

3.1 IO设备管理

3.1.1 IO设备

1.分类

块设备:信息交换以数据块为单位,属于有结构设备,比如磁盘等

字符设备:信息交换以自负为单位,信息没有固定结构,比如打印机,键盘等,使用流传输

2.IO接口(设备控制器)

IO接收器又称为设备控制器,位于CPU和设备之间,承担着CPU和设备之间通信的中介功能

(1)设备控制器和CPU的接口:包含三类控制线数据线、地址线和控制线。数据线通常和数据寄存器(存放从设备送来的输入数据和CPU送来的输出数据)以及控制/状态寄存器(存放从CPU送来的控制信息和设备送来的状态信息)

(2)设备控制器和设备的接口:一个设备控制器可以连接多个设备,每个接口中都存在着数据、控制和状态三种信号

(3)IO逻辑:用于实现对设备的控制。通过一组控制线和CPU交互,对从CPU收到的IO命令进行译码

主要作用:

1.接收和识别CPU发来的命令

2.数据交换

3.标识和报告设备的状态

4.地址识别

5.数据缓冲

6.差错控制

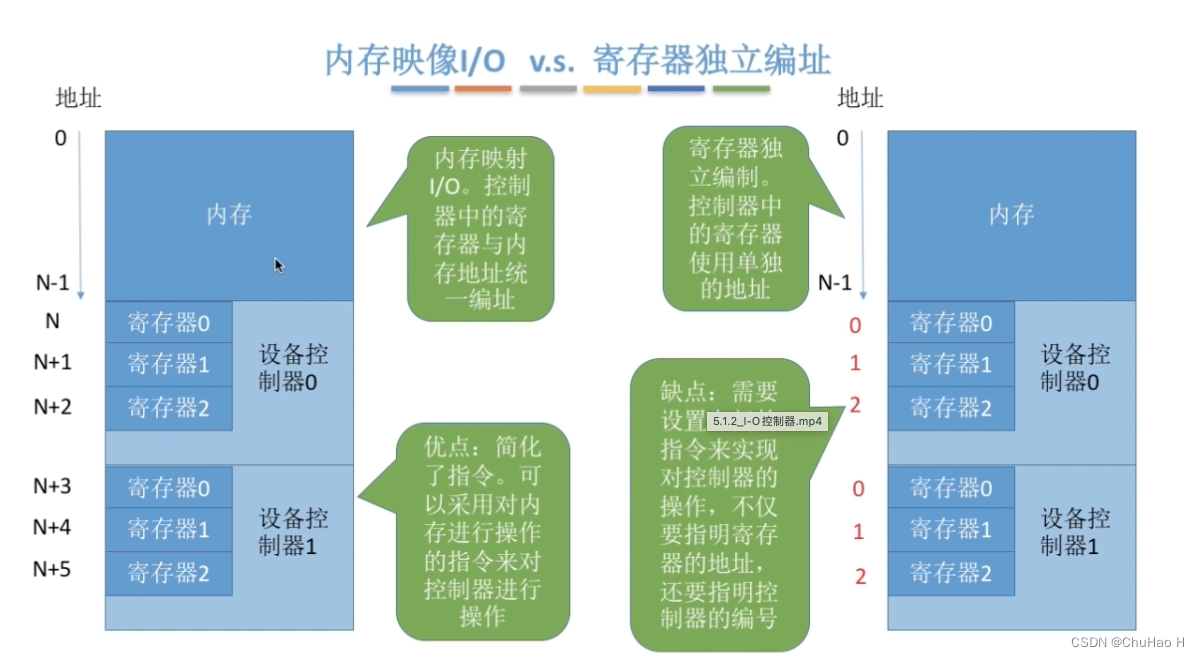

3.IO端口

IO端口指的是设备控制器中可以被CPU直接访问的寄存器,主要有三类

- 数据寄存器:实现CPU和设备之间的缓冲

- 状态寄存器:获取执行结果和设备状态信息

- 控制寄存器:由CPU写入的控制设备 的寄存器

为了实现CPU和IO端口的通信,一般由两种方法:

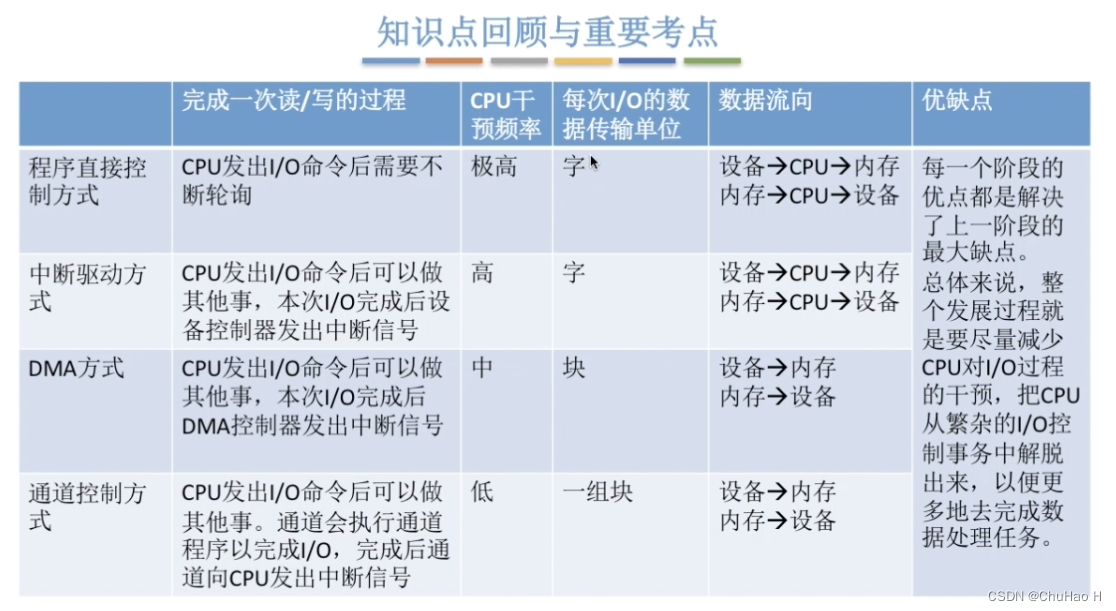

3.1.2 IO控制方式

1.程序直接控制

特点:每次只读写一个字

数据流向:

每个字的读写都需要CPU的帮助

优点:简单且易于实现

缺点:CPU和IO只能串行工作,CPU利用率低,CPU频繁轮询检查状态寄存器,干预频率高。

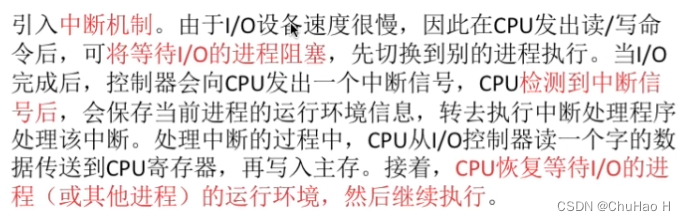

2.中断驱动方式

TIPS:

- CPU会在每个指令周期的末尾检查中断

- 中断会有一定开销

- 每次只读写一个字

- 每次读写都需要CPU干预

优点:CPU干预频率比1低,并且CPU和IO可以并行工作

缺点:每次只能传输一个字,并且频繁的中断会消耗CPU时间

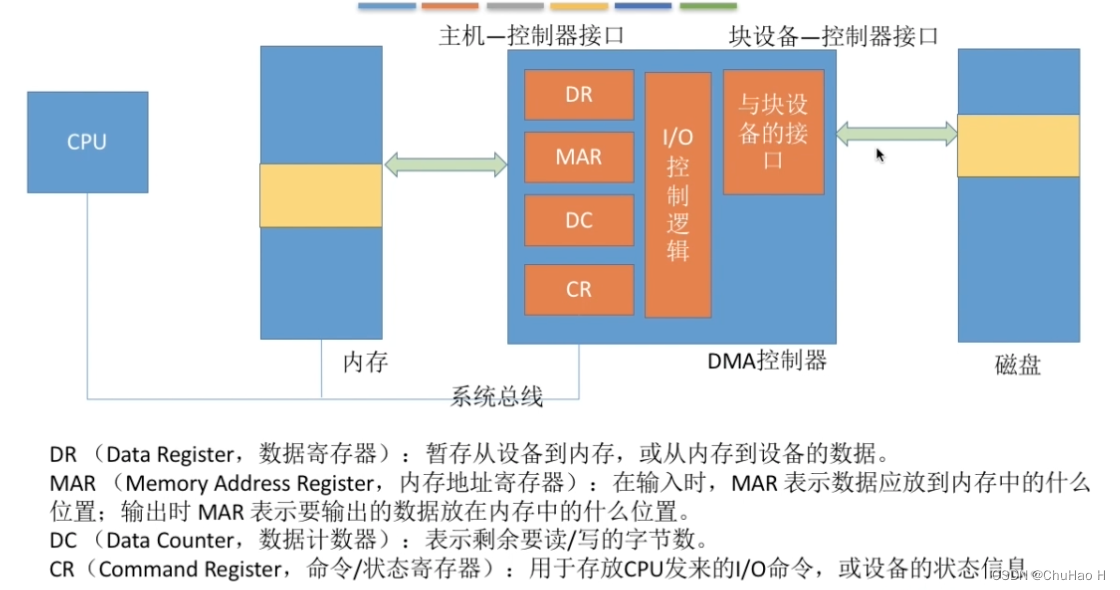

DMA方式(直接存储器存储)

DMA是一种特殊的控制器,主要用于对块设备的管理,有几个改进

- 数据传输单位是块

- 数据流向是设备直接传输到内存,而不经过CPU

- 仅在一个或多个块开始和结束时才需要CPU干预

可以看出,DMA控制器就像是一个中介,只需要CPU发出指令,他就可以完成将数据从IO到内存的迁移过程,而不需要CPU亲力亲为。

优点:数据传输以块为单位,CPU介入频率低,并行性得到提升

缺点:CPU每发出一条IO指令,只能读写一个或者多个连续的数据块。如果需要读写多个离散存储到数据块,或者要将数据分别写到了不同的内存区域时,CPU就要分别发出多条IO指令,进行多次中断处理。

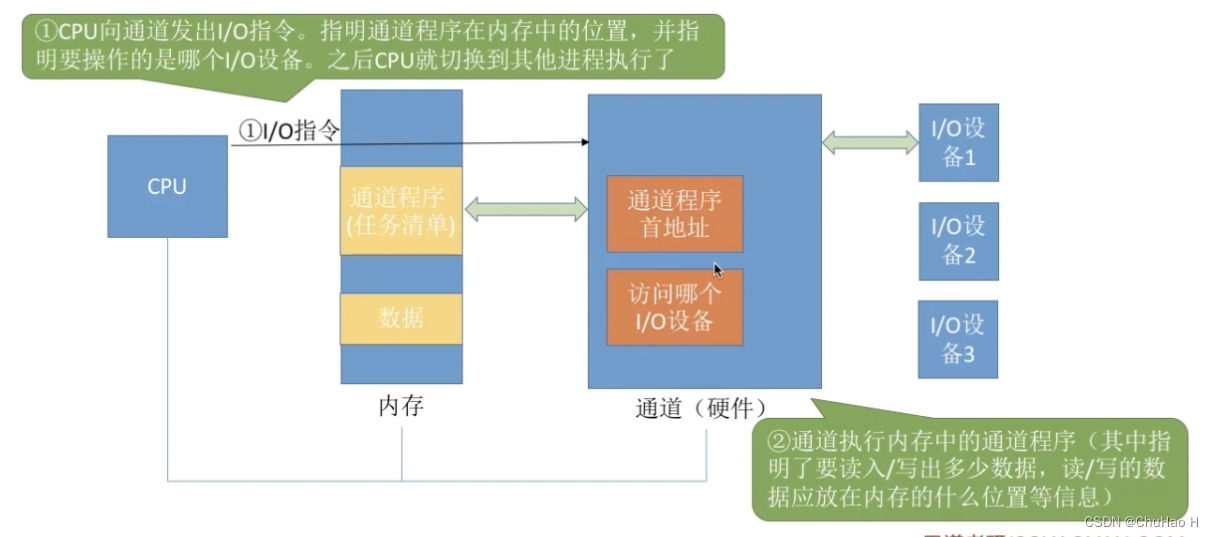

通道控制方式

通道,一种硬件,可以理解为弱鸡版的CPU,通道可以识别并且执行一系列的通道指令。

CPU干预频率很低,只需要将一组任务交给通道就可以去执行其他任务了。

同时,每次可以读写一组数据块。CPU、通道和IO可以并行工作,资源利用率高,但是实现较为复杂,需要专门的硬件支持,成本较高。

5.1.3 IO软件层次结构

| IO软件层次结构 |

|---|

| 用户层软件 |

| 设备独立性软件(内核) |

| 设备驱动程序(内核) |

| 中断处理程序(内核) |

| 硬件 |

用户层软件

提供与用户交互的接口,用户可以调用接口。将用户请求翻译成格式化的IO请求,并且通过系统调用请求操作系统内核服务

设备独立性软件

设备无关性软件,与设备的硬件属性无关的功能都在这一层实现是对底层的进一步抽象。另外还有差错控制和设备保护功能,以及设备的分配和回收和数据缓冲区管理。

建立逻辑设备到物理设备的映射,并且根据设备类型选择调用相应的驱动程序。设备独立性软件会通过逻辑设备表LUT确定对应物理设备

| 逻辑设备名 | 物理设备名 | 驱动程序入口地址 |

|---|

有的一整个系统只设置一张LUT,适用于单用户系统;多用户系统需要给每个用户分配一张LUT

设备驱动程序

驱动程序主要负责对硬件设备的具体控制,将上层发出的一系列指令转化为设备指令。

中断处理程序

IO任务完成时,IO控制器会发出一个中断信号,系统会根据中断信号类型找到相应的中断处理程序执行。

5.2 IO核心子系统

核心子系统主要包括设备独立性软件、设备驱动程序和中断处理程序三个