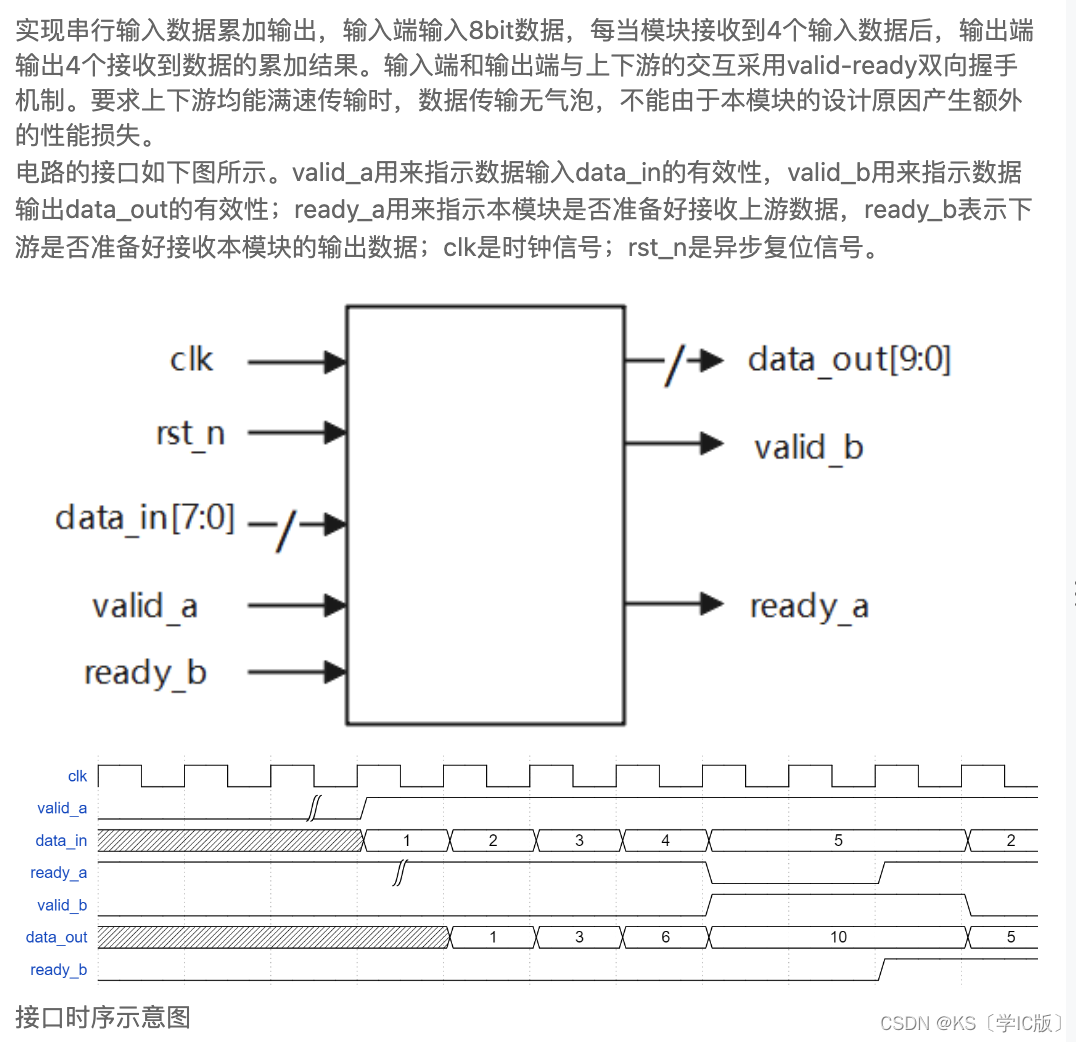

「Verilog学习笔记」数据累加输出

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

在data_out准备好,valid_b拉高时,如果下游的ready_b为低,表示下游此时不能接收本模块的数据,那么,将会拉低ready_a,以反压上游数据输入;

当下游ready_b拉高,且valid_b为高,表示模块与下游握手成功,valid_b在下一个时钟周期拉低;

当下游ready_b拉高,本来由于之前ready_b为低而反压上游的ready_a立即拉高,开始接收上游数据,注意,此细节,也是体现了题目要求的数据传输无气泡。如果ready_a不是立即拉高,而是在下一个时钟周期拉高,那么本模块将会在下游握手成功后空一个时钟周期,才能开始接收上游数据,这样是不满足题目要求的;

要实现4个输入数据的累加,要用1个寄存器将先到达的数据累加之后进行缓存。当上游握手成功,将输入数据累加进寄存器;当累加完4个输入数据,且下游握手成功,将新的输入数据缓存进寄存器。注意,之所以这样设计,是为了不造成性能损失,而之前的累加结果,已经传给了下游。

需要计数器来计数接收到的数据数量,计数器在0-3之间循环。计数器初始值是0,每接收一个数据,计数器加1,当计数器再次循环到0时,表示已经接收到4个数据,可以输出累加结果。

对于ready_a输出信号的产生,如果下游ready_b拉高,表示下游可以接收模块输出数据,那么此时ready_a应拉高,即本模块可以接收上游数据;如果没有接收够4个数据,即valid_b未拉高,那么表示本模块仍可以接收上游数据此时ready_a应拉高。所以综上所述,ready_a信号的产生采用组合逻辑产生。

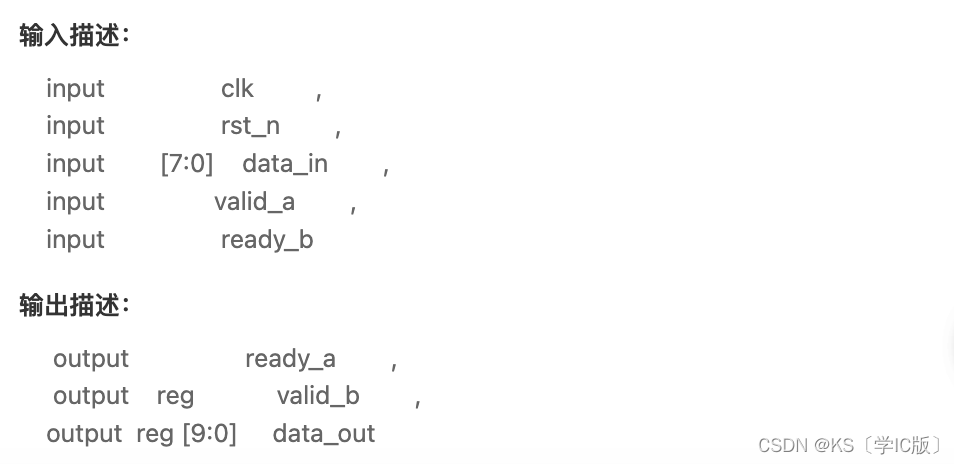

`timescale 1ns/1nsmodule valid_ready(input clk , input rst_n ,input [7:0] data_in ,input valid_a ,input ready_b ,output ready_a ,output reg valid_b ,output reg [9:0] data_out

);reg [1:0] data_cnt ; assign ready_a = !valid_b | ready_b ; always @ (posedge clk or negedge rst_n) begin if (~rst_n) data_cnt <= 1'd0 ; else if (valid_a && ready_a) data_cnt <= (data_cnt == 2'd3) ? 1'd0 : (data_cnt + 1'd1) ;endalways @ (posedge clk or negedge rst_n) begin if (~rst_n) valid_b <= 1'd0 ; else if (data_cnt == 2'd3 && valid_a && ready_a) valid_b <= 1'd1 ; else if (valid_b && ready_b) valid_b <= 1'd0 ; endalways @ (posedge clk or negedge rst_n) begin if (~rst_n) data_out <= 1'd0 ; else if (ready_b && valid_a && ready_a && (data_cnt == 2'd0)) data_out <= data_in ; else if (valid_a && ready_a) data_out <= data_out + data_in ; endendmodule