RH850P1X芯片学习笔记-Overview

文章目录

- Outline

- 产品列表

- 功能框图

- 特点

- Pin和引脚功能

- CPU系统

- CPU

- FPU浮点运算单元

- 中断处理

- 保护机制

- 指令缓存

- Local RAM

- Global RAM

- 处理器间通信和相互排斥机制

- 操作模式

- 中断功能

- DMA

- 电源供电

- Reset控制单元

- 时钟控制单元

- CSIH-SPI

- MCAN

- 看门狗计时器

- 系统计时器

- GTM通用定时器模块

- 外设互联PIC

- A/D转换器

- 功能安全

- ECM错误控制模块

- Data CRC功能

- CVM内核电压监控

- 时钟监控

- Flash内存

- RAM模块

- 基础安全

- ICUMC

- 缩写列表

Outline

RH850/P1x-C是一个32位单芯片微电脑,具有多核CPU、Code Flash、Data Flash、RAM模块、DMA控制器、许多用于汽车应用的通信接口、A/D转换器、定时器单元等。该芯片是面向符合功能安全标准(ISO26262)的汽车应用的。

主要包含以下模块:

1.RH850多核CPU

该芯片根据产品类型配备了一个或两个RH850 G3M单元作为主CPU,每个CPU单元都有锁定双核功能,以保证功能安全。除此之外,该芯片还配备了一个RH850 G3K单元作为子CPU,控制安全功能(取决于产品类型)。这些CPU的结构通过2字节的基本指令和面向高级语言编译器的指令集实现了程序的紧凑占用。这些CPU具有非常快的中断响应时间,因此它们可以支持硬实时应用.

P1M-C只有一个RH850 G3M核,P1H-C有两个RH850 G3M核

2.片上Code Flash与Data Flash

P1H-C最大支持8MB Code flash,P1M-C 2MB Code flash

P1H-C最大192+32 KB Data Flash,P1M-C 64+32 KB Data Flash

3.丰富的外设功能

该芯片不仅配备了常见的通信接口,如SPI和HS-USRT,还配备了面向汽车的接口,如MCAN、FlexRay、RLIN、SENT。此外,它还支持以太网(取决于产品类型)。作为内部外设模块,该芯片有A/D转换器、系统定时器、通用定时器模块和专用的外设互连模块,这些模块连接这些外设的功能。

4.功能安全支持

芯片配备几个专门的功能,包括CPU的锁步双核配置、带ECC的内存保护、带ECC的总线保护、外围模块保护和电压/时钟监控,以支持汽车应用中要求的功能安全标准(ISO26262)

5.信息安全支持

该芯片支持各种安全功能(取决于产品类型)。智能加密单元-主控(ICUMC)有一个专门的安全CPU(RH850G3K)和一些安全外设,如AES引擎和随机数字发生器(RNG)。该芯片还实现了非安全域和安全域之间的HW级域分离。内部资源如代码和数据flash可以被分配到任何一个域,安全域受到硬件机制的保护,防止非安全访问。该芯片还具有对来自外部的恶意访问的保护方案

产品列表

详细产品参数:

P1H-C的CPU频率最高240M,且只能为160M或240M

MCAN表示普通CAN,M_TTCAN表示可以支持CAN-FD

按上面的产品list来看,1372只有两路普通can,1372A多一路CAN FD

内核供电1.25V,I/O和ADC供电3.3V

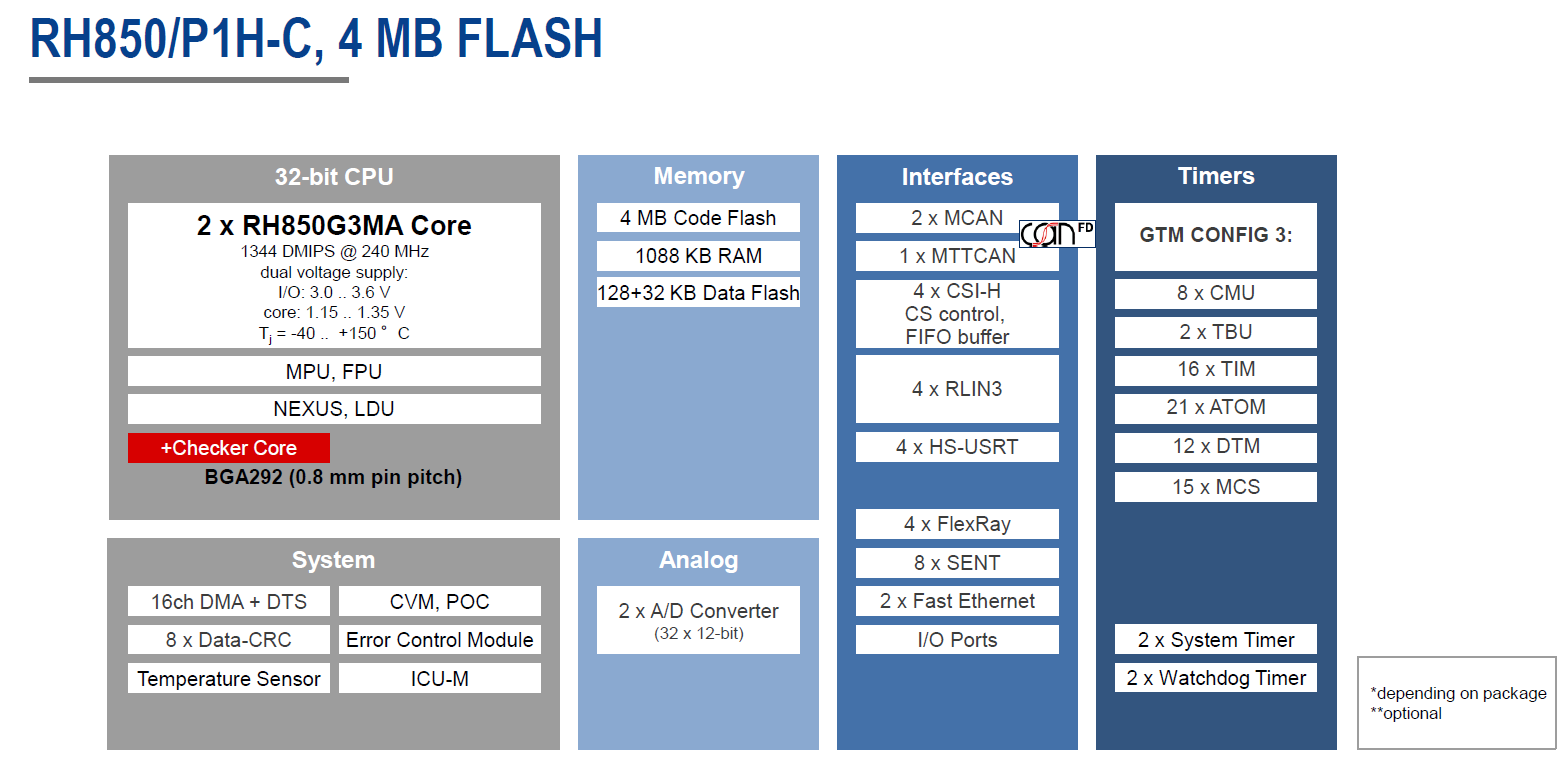

功能框图

特点

Pin和引脚功能

- 大多数数字引脚都有可选择的功能,包括多达9个专用功能(每个输入和输出和一个特殊功能有多达4个备选功能)和一个通用I/O端口。

- 可选择输出引脚的驱动能力

- 可选择输入引脚的上拉/下拉/关闭

- 通用I/O端口可由多CPU按引脚访问而不相互排斥

CPU系统

CPU

- 用于嵌入式控制器的高性能32位架构

- 32位内部数据总线

- 32个32位通用寄存器

- RISC类型指令集

- 长/短格式的加载/存储指令

- 三个操作数指令

- 基于C语言

- 操作模式: 用户模式/主管模式

- 地址空间:4GB的数据和指令的线性地址空间

FPU浮点运算单元

- 支持单精度(32位)和双精度(64位)

- 支持符合IEEE754标准的数据类型和异常

- 舍入模式: 四舍五入模式:最接近/趋于0/趋于+∞/趋于-∞

- 处理非标准化的数字: 截断到零/符合IEEE754的异常

中断处理

- 可以为每个中断通道指定16个中断优先级

- 两种中断处理程序地址计算方法

直接向量法

表参考法 - 用于快速上下文切换的PUSHSP和POPSP指令

保护机制

- 内存保护单元(MPU)保护内存区域免受软件的非法访问。

- 内部外设保护装置(IPG)保护内部外设的寄存器不被软件非法访问。

- PE Guard (PEG)保护本地RAM和内部外设寄存器,防止外部总线主站的非法访问。

- 全局RAM (GRAM) Guard保护GRAM区域,防止所有总线主站的非法访问

指令缓存

每个CPU都有自己的指令缓存,用于Code Flash

Local RAM

每个CPU都有自己的Local RAM

Global RAM

每个CPU都可以访问Global RAM

处理器间通信和相互排斥机制

- 处理器间中断寄存器(IPIR)

- 信号量Semaphore寄存器

- CAXI(比较和交换联锁),LDL.W(加载链接字)和STC.W(存储条件字)指令

操作模式

- 工作模式

正常工作模式

串行闪存编程模式

边界扫描模式 - 模式设置

由模式选择引脚设置: FLMD0, FLMD1, MODE0, MODE1 (FLMD1, MODE0, MODE1也可以作为GPIO使用。)

在上电复位或系统复位时锁住 1

中断功能

- 三种类型的中断

- FENMI:FE级不可屏蔽中断

- FEINT:FE级可屏蔽中断

- EIINT:EI级可屏蔽中断

- 每个中断独立的16个优先级

- 每个中断独立的可屏蔽

- 每个中断独立的16个优先级

- FENMI:FE级不可屏蔽中断

- 中断控制器

- 主中断控制器(INTC1)

- 每个CPU(PE1和PE2)有自己的INTC1。

- 直接处理多达2个FE级中断和多达32个EI级中断

- 主中断控制器(INTC1)

- 次要中断控制器(INTC2)

- 由两个CPU共享

- 通过INTC1通知CPU多达224个中断

- 每个中断可以独立地映射到只有一个CPU或两个CPU并行地处理

DMA

- 两种类型的DMA引擎: DMAC和DTS

- DMAC

- 传输信息存储在DMAC控制寄存器中。

- 多达16个通道(每个通道有1个寄存器组)

- 多达128个DMA触发源

- DTS

- 传输信息存储在专用SRAM(DTSRAM)中。

- 多达128个通道可以同时活动。

- 多达128个DTS请求

- DMAC

- 地址空间:4GB

- 传输模式: 单一传输,块传输1,块传输2

- 传输数据大小:1/2/4/8/16字节

- 中断: 传输完成中断,传输计数匹配中断

- 支持重新加载功能

- 支持链式功能

电源供电

- 双电源(DPS)

- 用于安全启动的内部POC(上电清除)

- 用于监测内部电源电压(VDD)的内核电压监控器(CVM)

Reset控制单元

- 6个复位功能

- 开机复位

- 系统复位1

- 系统复位2

- 应用复位1

- 限制复位

- debug复位

- 外部输出引脚: RESETOUTZ

- 某种复位后自动进行RAM初始化

- 某种复位后自动执行HW BIST

时钟控制单元

- 片上晶体谐振电路(主OSC)

- 片上内部晶振,在时钟启动时用作备份时钟,并用于安全目的

- 片上PLL,从主OSC产生高速内部时钟

- 时钟频率

- 主OSC:16/20/24MHz

- 内部晶振: 16MHz

- 由PLL产生的内部时钟:高达240MHz

- 两个软件可配置的外部时钟输出

- 软件可配置的时钟分频器,实现灵活的时钟档位功能

CSIH-SPI

- 三线串行同步数据传输,被称为SPI

- 全双工操作(同时传输和接收),仅接收模式,或仅传输模式

- 主模式和从模式可选

- 每个芯片选择的时钟和数据相位可选

- 每个芯片选择的数据传输MSB或LSB优先可选

- 每个芯片选择的传输数据长度可从2到16位选择,以1位为单位

- EDL(扩展数据长度)功能用于传输16位以上的数据

- 最大传输速率:主模式下最大20Mbit/s,从模式下最大的20Mbit/s

- 可通过BRG输出(在主模式下)或从属时钟选择比特率

- 可选择发送模式、接收模式和发送/接收模式

- 缓冲区大小为128字(1字为数据32位+ECC 7位)

- 可选择内存模式(FIFO、双缓冲区、仅Tx的缓冲区、 内置握手功能

- 错误检测(数据一致性检查、奇偶校验、超时、超限)

- AUTOSAR的JOB使能控制位

- 广播的RCB(递归配置)位

- 用于自检的LBM(回环模式)功能

- 四个不同的中断请求信号(INTCSIHnTIC、INTCSIHnTIR、INTCSIHnTIRE、INTCSIHnTIJC)

- IDLE状态控制功能

- 用于延长空闲时间的静音模式通信

- 自动生成具有可配置有效电平的芯片选择输出信号

- 无需激活芯片选择的数据传输

- 每个芯片选择的传输速度可从四个预定义的波特率中选择(在主模式中)或通过来自主模式的时钟输入信号(在从模式中)

- 对所有CSIH寄存器提供全面的DMA支持

MCAN

- 符合ISO 11898-1

- 数据传输率高达1Mbps,单独用于每个CAN通道。对于CAN FD,高达8Mbps

- 可选择的ID类型 - 11位标准ID - 11位标准ID + 18位扩展ID

- 消息缓冲区

- 多达64个专用接收缓冲区

- 多达32个专用发送缓冲区

- 支持所有AUTOSAR要求

- 发送中止中断

- 非等待处理功能

- 包括2个以上的TX缓冲区的优先级

- 支持几种自我测试的措施: 外部和内部回环

- 改进的RX系统

- 可扩展的RX FIFO结构,每个FIFO最多有64个CAN Buffers

- RX时间戳

- RX FIFO超时中断

- FIFO填充电平中断

- 改进的TX系统

- FIFO填充电平监督(中断)

- 支持发送取消以避免 “内部优先级倒置”

- 结合消息缓冲区和TX FIFO及TX队列概念

- 高优先级消息的专用TX消息缓冲区

- TX缓冲区间的ID优先级、 TX队列缓冲区和最老的TX FIFO元素之间的ID优先级

- 传输暂停以分离两个连续的TX消息

- FIFOs

- 两个可配置的接收FIFO

- 可配置的发送FIFO

- 可配置的发送队列

- 可配置的发送事件FIFO

- 增强的接收过滤

- 支持11位和29位CAN标识符,每个过滤元件可配置为接受/拒绝

- 每个条目的29位CAN标识符接受过滤掩码可编程

- 每个接受过滤元件针对FIFO 0或1或专用RX Buffer

- 每个FIFO或RX Buffer过滤元件可作为一个从到范围过滤器使用、 每个FIFO或RX缓冲器的过滤元件都可以作为一个从头到尾的过滤器,作为一个或两个专用ID的过滤器或作为一个经典的位掩码过滤器

- 每个过滤元件都可以单独启用/禁用

- 根据ISO11898-4支持TT_CAN level 2

- 支持AUTOSAR的Pretended Networking

- 支持时间戳功能

看门狗计时器

- 一个CPU一个通道

- 可选择固定激活码和可变激活码(VAC)

- 有两种计数器启动模式

- 自动(默认)启动模式

- 软件触发启动模式

- 检测到错误时产生错误信号给ECM

- 在计数器溢出值的75%时产生中断请求

- 刷新窗口功能

系统计时器

- 一个64位的计数器,可作为一个长周期的时间戳

- 三个32位的计数器

- 每个计数器有四个比较寄存器

GTM通用定时器模块

GTM是一个模块化的定时器单元,用于支持底盘控制应用,将CPU从高中断负载中卸载下来。GTM的大部分任务可以独立于CPU运行。根据产品类型,实现了两种不同的GTM配置

外设互联PIC

外围互连(PIC)将一些外围设备相互连接起来,以实现独立功能的增强。

- ADCF触发选择功能

- 信号路由功能,用于:

- ADCF转换中断路由到GTM输入

- 用于PWM诊断的GTM输出监控

- 用于GTM输出的外部引脚的Hi-Z控制功能

- UART(RLIN3)的波特率测量

A/D转换器

- 基于逐次逼近法(SAR-ADC)的A/D转换

- 12位分辨率

- 最小转换时间:1us。

- 虚拟通道概念

- 支持扫描组

- 两种扫描模式: 多周期扫描模式和连续扫描模式

- 异步/同步暂停和恢复功能

- 支持中断和DMA传输。

- A/D转换值添加功能

- 可设置模拟转换电压范围。

- 提供丰富的安全功能

功能安全

- 开发符合ISO26262功能安全标准。

- 主要的安全机制

- 纠错码(ECC)和错误检测码(EDC)

- 冗余数据处理单元(CPU,DMA)与比较单元的锁定功能

- 内存保护单元(MPU)和处理器元件(PEG)、内部外设模块(IPG)、全局RAM(GRG)和外设总线(PBG)的从动防护

- 启动测试时的现场BIST

- 错误控制模块(ECM)、 核心电压监控器(CVM)

- 时钟监控器(CLMA)

- 看门狗定时器(WDTA)

- 数据CRC(DCRB)

- 三重模块化冗余(TMR)寄存器,用于独立应用部分,以确保对单一事件影响(SEE)引起的瞬时故障的稳健性

- 安全导向的芯片布局

ECM错误控制模块

错误控制模块(ECM)通过来自各种错误源和监控逻辑的错误输入信号产生错误信号到外部MCU、中断和复位请求。

- 针对每个错误原因产生中断请求

- 针对每个错误原因产生内部复位(系统复位2)请求

- 针对错误原因产生错误信号,该信号连接到专用数字输出终端

- 可确认当前错误状态。

- 实现自我诊断功能。

- 中断处理的超时功能

- ERROROUTZ释放定时器 等待时间可由SW配置。在配置的时间过后,ERROROUTZ可以被SW设置为高电平。

- 用PIC对GTM定时器输出终端进行Hi-Z控制

- 当ECM捕捉到与安全有关的错误时,GTM定时器输出终端将通过ECM的低电平输出而被Hi-Z。

Data CRC功能

- 支持以下四种符合AUTOSAR标准的CRC发生器多项式

- 32位以太网CRC

- 16位CCITT CRC

- 8位SAE J1850 CRC

- 8位0x2F多项式CRC

CVM内核电压监控

- CVM监控核心电压的过高和过低。

- 违反核心电压的工作范围会被告知:

- 单个输出引脚(CVMOUTZ)。

- 核心电压过高和过低的标志

- CVM复位

- 除了诊断功能外,CVM的功能与内部或外部的RESET无关,除了开机复位。

- 诊断功能:

- CVM功能是可以测试的。

- 在不影响核心电压本身的情况下,可以产生过压和欠压错误。

- CVM错误测试是通过改变参考电压完成的。

- 对于诊断来说,通往CVMOUTZ引脚的信号路径可以被屏蔽。

- CVMOUTZ引脚提供回读功能以检查引脚水平。

时钟监控

- 根据设备配置,最多可有六个时钟监视器。

- 检测导致频率低于或高于目标频率的时钟干扰,并向ICUMC的ECM和INTC发送错误通知

- 支持自诊断功能

Flash内存

- Code Flash

- 容量:在生产设备中高达8MB,在仿真设备中高达10MB

- 双CPU设备(P1H-C和P1H-CE)中的双库配置

- 编程单元:256字节,擦除单元: 8KB或32KB(取决于块)

- 支持每块OTP(一次性可编程)

- 支持每块写保护

- 安全特性

- 非安全区和安全区之间可配置的区域分隔

- 调试模式下的密码保护

- Data Flash

- 容量:非安全区域高达192KB,安全区域为32KB* 1

- 编程单元: 4字节,擦除单元: 64字节

- ECC支持错误检测和纠正

- 编程方法

- 来自外部闪存写入器的串行编程模式

- 来自内部CPU的自编程模式

- 支持BGO(BackGround Operation)

- 在Data Flash P/E期间可以读取Code Flash

- 当闪存在bank中被擦除/编程/读取时,另一个bank中的闪存,可以被擦除/编程/读取。

- 用于存储系统配置参数的额外区域

注:在非安全应用的情况下,安全区域的Data FLash可以作为普通Data Flash使用

RAM模块

- 主CPU(PE1和PE2)

-本地RAM(LRAM)

-指令缓存(标签和数据) - ICUMC

- 本地RAM(LRAM)

- 指令缓存(标签和数据)

- 全局RAM(GRAM)

- 仿真RAM(ERAM)(仅P1H-CE)

- FCU RAM

- 外设模块

- DTS RAM

- CSIH RAM

- MCAN RAM

- FlexRay RAM

- Ethernet RAM

- GTM RAM

- 功能安全的错误检测和纠正

- LRAM、GRAM和外围RAM复位后的自动RAM初始化(例外:PE1中LRAM的头部1KB、FCU RAM、ERAM和以太网RAM)

基础安全

- 安全域和非安全域之间的HW级域分离

- 闪存保护

- 模式进入保护

- 调试器验证

- 设备退化由闪存配置选项控制

- 安全看门狗定时器

- 缓存保护

- 复位后的RAM初始化

ICUMC

- 用于安全应用的专用CPU(RH850 G3K)(取决于产品类型)

- 安全中断处理

- 专用安全外设

- AES引擎

- 随机数字发生器(RNG)

- 计时器

- 看门狗计时器

- 工具连接的额外认证,如调试器

没有用到的先不看

缩写列表

| 全名 | 缩写 |

|---|---|

| External Memory Controller外部存储控制器 | MEMC |

| Interrupt Controller中断控制器 | INTC |

| Direct Memory Access ControllerDMA控制器 | DMAC |

| Data Transfer System数据传输系统 | DTS |

| Clocked Serial Interface H | CSIH,也就是SPI |

| High-Speed Universal Synchronous Receiver / Transmitter高速串口 | HS-USRT |

| FlexRay | FLX |

| Ethernet Controller以太网控制器 | ETNA |

| Window Watchdog Timer窗口看门狗定时器 | WDTA |

| System Timer | STM |

| Generic Timer Module | GTM |

| Peripheral Interconnect外设互连 | PIC |

| AD Converter | ADCF |

| Error Control Module | ECM |

| Data CRC Function | DCRB |

| Core Voltage Monitor内核电压监控 | CVM |

| Clock Monitor | CLMA |

| Temperature Sensor | OTS |

| On-Chip Debug | OCD |

| Emulation Device 仿真设备 | ED |

| Intelligent Cryptographic Unit – Master智能加密单元-主机 | ICUMC |