AXI4-Stream Interconnect IP核(1)——原理

一、概述

AXI4-Stream Interconnect 是复杂片上系统(SoC)和现场可编程门阵列(FPGA)应用设计中的关键组件,它负责在系统内部不同模块之间路由数据流。AXI4-Stream协议是ARM引入的AMBA(高级微控制器总线架构)规范中的AXI(高级可扩展接口)家族的一部分。AXI4-Stream专为高速、单向数据传输而设计,用于主从组件间的数据传输,无需地址。

AXI4-Stream Interconnect IP 提供了高度灵活且可配置的数据流管理功能,支持复杂的系统设计需求,这些功能包括:

可配置的多主到多从(最多16x16)交叉点开关:这意味着该IP支持最多16个主设备与最多16个从设备之间的连接,提供了高度的灵活性和扩展性。

任意TDATA字节宽度转换:TDATA是AXI4-Stream中用于传输数据的信号,此功能允许在不同模块之间自动调整数据宽度,即使它们处理的数据宽度不同。

同步和异步时钟率转换:该IP能够在具有不同时钟域的模块之间传输数据,不论这些模块是同步还是异步操作。

可配置的数据路径FIFO缓冲区:包括支持存储转发(数据包)的FIFO缓冲区。FIFO(先进先出)缓冲区对于管理数据流、缓解背压和优化数据传输效率至关重要。

边界处可选的寄存器切片以便于时序收敛:在IP的输入和输出边界处可以添加寄存器切片,这有助于优化时序,特别是在高速或复杂设计中,时序收敛可能较为困难。

支持多时钟域:这一特性允许AXI4-Stream Interconnect IP在设计中使用多个时钟源,每个源可以有不同的频率。

二、详细说明

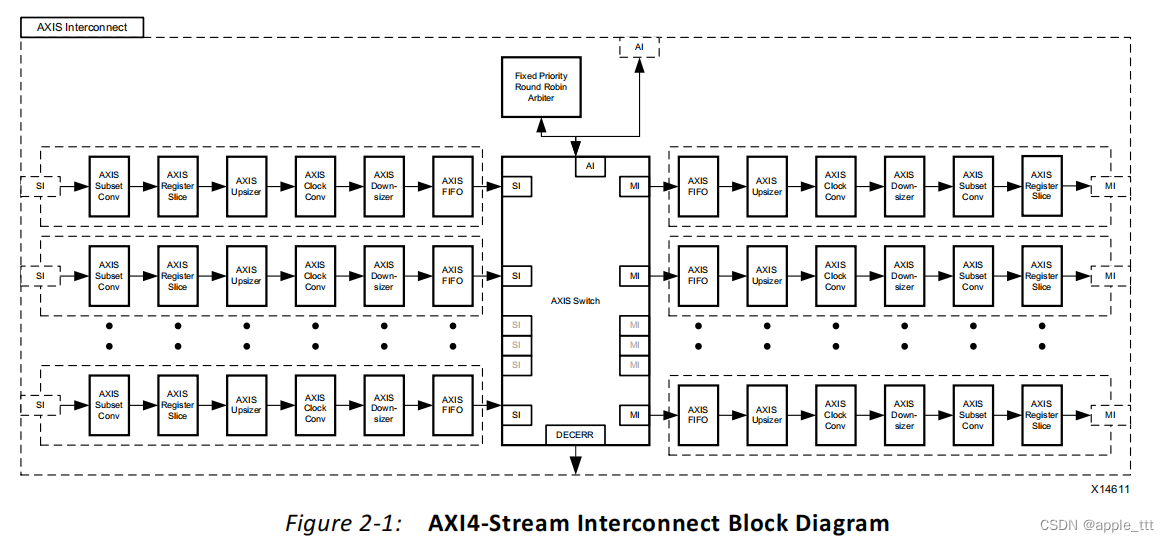

AXI4-Stream Interconnect 核是围绕AXI4-Stream交换器构建的一系列子模块的集合。在交换器的之前和之后,有一些子模块被分组到数据路径中,以便进行数据操作和流量控制。每个独立的子模块都包含符合AXI4-Stream协议的主接口和从接口。下图能够清晰地说明AXI4-Stream Interconnect 内部结构和工作原理。

AXI4-Stream Switch支持最多16个主端到16个从端的交换配置。如上图所示,一个 AXI4-Stream 主端可以连接到 AXI4-Stream 互连的从接口(SI),同样地,一个AXI4-Stream 从端可以连接到 AXI4-Stream 互连的主接口(MI)。

AXI4-Stream Interconnect 中提供了若干的子模块,这些子模块可以根据参数选择实例化,使得该IP核在设计上具有充分的灵活性。

| 子模块名称 | 描述 | 推断(Inferred)或显式(Explicit)实例化 |

| Subset Converter (子集转换器) | 从AXIS总线接口中添加或删除可选信号。 | 在一些AXI4-Stream Interconnect的实现中,当存在数据宽度转换器并且TID、TDEST或TLAST信号被使用时,TKEEP信号可能会被有限推断(Limited Inference)。 |

| Register Slice (寄存器切片) | 提供一种机制来桥接不同ACLK域内的主/从之间的连接。 | 推断 |

| Data Width Converter (数据位宽转换器) | 通过将多个传输聚合到一个传输中,允许扩展AXIS TDATA宽度,或者通过将一个传输分割成更小的TDATA宽度的多个传输来减少AXIS TDATA宽度。 | 推断 |

| Data FIFO (数据FIFO) | 提供AXIS数据存储。 | 显式 |

| Switch (交换器) | 允许从多个主机路由到多个从机。 | 当系统中存在多个主或多个从时推断。 |

2.1 AXI4-Stream Switch and Arbiter(AXIS交换机和仲裁器)

AXI4-Stream Switch支持1:N、M:1和M:N配置,能够将最多16个主设备连接到16个从设备。在1:N和M:N配置中,需要AXI4-Stream的TDEST信号来指导数据流的路由。

我们举个例子来理解一下TDEST信号的工作方式:

假设有一个设计,其中 AXI4-Stream Switch 需要将数据从四个不同的主设备(M1, M2, M3, M4)路由到两个从设备(S1, S2)。为了简化说明,我们只考虑 TDEST 范围的配置和路由决策。

配置示例

主设备 M1 被分配了 TDEST 范围 0-15,意味着它发送的所有数据流,其 TDEST 值在这个范围内,都将被路由到一个特定的目的地。

主设备 M2 被分配了 TDEST 范围 16-31。

主设备 M3 和 M4 分别被分配了类似的方式。

路由决策

假设 S1 处理的是 TDEST 范围 0-15 和 32-47 的数据流,而 S2 处理的是 TDEST 范围 16-31 和 48-63。

数据流处理

当 M1 发送一个带有 TDEST=10 的数据流时,因为这个值落在其分配的范围内,且根据配置,这个范围的数据应被路由到 S1,所以数据流将成功路由到 S1。

如果 M2 发送一个带有 TDEST=20 的数据流,根据配置,这个数据流将被路由到 S2,因为 TDEST=20 落在为 S2 配置的范围内。

假设 M1 错误地发送了一个带有 TDEST=50 的数据流(这个值不在它的分配范围内),因为没有主设备被分配了这个 TDEST 范围,所以这个数据流会触发解码错误并被丢弃。

内部仲裁器可以执行固定优先级仲裁或RR轮询仲裁。仲裁器/交换机可以基于每次传输或在数据包边界(通过TLAST信号或在一定数量的活跃或空闲传输后)进行仲裁。

2.2 AXI4-Stream Clock Converter(AXIS时钟转换器)

在 AXI4-Stream 协议中,时钟转换器是必需的,它用于将不同时钟频率下运行的主设备转换为从设备。通常,AXI4-Stream 交换机应该与最快的从设备同步时钟频率;不在该频率下运行的设备需要进行时钟转换。

同步时钟转换器是理想的选择,因为它们具有最低的延迟和较小的面积。然而,只有当两个时钟相位对齐、时钟比率为整数,并且能够满足最大频率(fmax)要求时,同步时钟转换器才是可行的。

异步时钟转换器是一种通用解决方案,能够处理同步/异步时钟和任意相位对齐的情况。这种方案的权衡在于,与异步时钟转换器相关联的面积和延迟显著增加。如果配置了全局时钟使能,将生成额外的逻辑来独立处理每个时钟域的时钟使能信号。每个数据路径中都有一个时钟转换器模块,如果时钟被指定为异步或具有不同的同步时钟比率,则会实例化该模块。时钟转换器模块执行以下功能:

- 一个时钟速率降低模块,执行从其输入(SI)侧到输出(MI)侧的整数(N:1)除法时钟速率降低。

- 一个时钟速率加速模块,执行从其输入(SI)侧到输出(MI)侧的整数(1:N)乘法时钟速率加速。

- 在输入和输出之间使用内部 FIFO 生成器实例化模块进行异步时钟速率转换。

- 处理不同 ACLKEN 信号的时钟使能交叉逻辑,适用于每个时钟域。

通过这些机制,AXI4-Stream 协议能够在具有不同时钟域的系统内有效地传输数据,同时保持数据的完整性和同步,但这需要对时钟转换策略和硬件资源的仔细规划和管理。

2.3 AXI4-Stream Data Width Converter(AXIS数据位宽转换器)

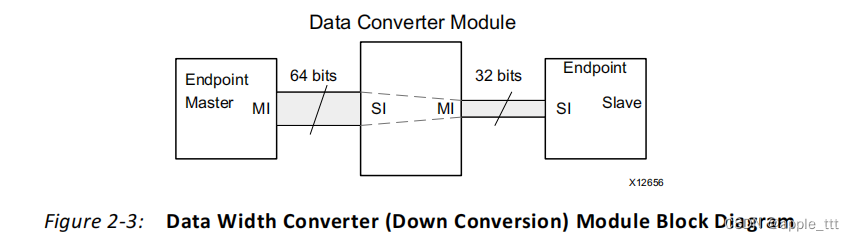

在 AXI4-Stream 协议中,数据宽度转换器(增宽器/缩小器)允许不同数据宽度的核之间进行通信。转换器能够处理从 1-256 字节到 2-512 字节的上转换,以及从 2-512 字节到 1-256 字节的下转换。对于非整数倍的字节比率转换(N:M),首先计算 N 和 M 的最小公倍数(LCM),然后通过两个步骤完成转换:先从 N:LCM 上转换,再从 LCM:M 下转换。上转换的最小延迟为 2 + N 个时钟周期,而下转换的最小延迟为两个时钟周期。

2.4 AXI4-Stream Register Slice(AXIS寄存器切片)

寄存器切片是一种多用途的流水线寄存器,能够隔离主设备和从设备之间的时序路径。设计寄存器切片的目的是在时序改进与所需的面积及延迟之间进行权衡,以形成符合协议的流水线阶段。作为一个两级深的 FIFO 缓冲区实现,寄存器切片支持由主设备(通道源)和/或从设备(通道目的地)进行节流,同时能够实现背靠背传输而不引入不必要的空闲周期。该模块可以在所有端口边界独立实例化。

2.5 AXI4-Stream Data FIFO Buffer (AXIS数据FIFO缓冲)

FIFO(First-In, First-Out)模块在 AXI4-Stream 数据的临时存储(缓冲)中起到重要作用。当需要比寄存器切片更多的缓冲时,或者在存储-转发场景下(即,在将数据从主设备转发到从设备之前积累一定数量的字节时),应该在两个端点之间使用 FIFO 缓冲模块。

FIFO 模块也能够实现异步时钟转换。因此,当在同一接口上启用异步时钟转换和 FIFOs 时,不会实例化冗余的 FIFOs。FIFO 模块使用 Xilinx® LogiCORE™ IP FIFO 生成器模块,支持native AXI4-Stream,并具有以下特点:

- 可变的 FIFO 深度。

- FIFO 数据宽度从 8 到 1,024 位。1,024 位的 FIFO 数据宽度限制是由 FIFO 生成器的限制造成的,这限制了在 FIFO 中缓冲的传输的有效负载宽度。这一限制可能会在未来的 FIFO 生成器版本中被取消,届时,AXIS FIFO 也将支持对有效负载宽度高达 4,096 位的传输的 FIFO 缓冲。FIFO 的宽度由 SWITCH 组件的宽度决定。

- 独立或共用的时钟域。

- 对称的长宽比。

- 异步低电平复位。

- 可选的存储类型。对于深度 32 或更少的,存储类型被推断为分布式块 RAM,对于所有其他情况,则为块 RAM。

- 以首字下落模式(FWFT, First-Word Fall-Through)操作。

- 占用率接口。

- FIFO 生成器的 rd_data_count 和 wr_data_count 作为分别同步到读侧和写侧时钟域的独立输出传递。

FIFO 模块提供了灵活的数据缓冲和流控制能力,特别是在处理不同速率或需要数据积累的场景中,是系统中不可或缺的组件。