ZYNQ之路--带你弄明白Vivado设计流程

目录

界面介绍

设计流程

设计

综合

实现

生成比特流

其它

结尾

哈喽大家好,这一篇ZYNQ之路我想给大家介绍一下Vivado的入门级使用。为什么要写这篇博客呢?

当然不是因为水啦!

作为一名初学者,用惯了Quartus的我刚开始对于Xilinx的开发工具家族是十分迷惑的,什么Vitis和Vivado都是干嘛的?等等诸如此类的问题,最重要的是网上并没有介绍这些软件关系的资料(当然了,可以参考我这篇博客)

经过一段时间的摸索,我大概对于使用这些软件有了一些心得体会,所以为什么要写这篇博客呢?当然是因为网上有关的内容太少了。各类五花八门的教材打着教会你ZYNQ的旗子,实际上做的都是一些填鸭式的教学,我们往往只知其然而不是所以然,不得其精髓,这是我们应该避免的。

从我个人角度出发,我认为掌握Vivado软件的使用思路,比学会点亮一个LED灯所带来的意义大多了,所以下面且听吾言之一二吧!

界面介绍

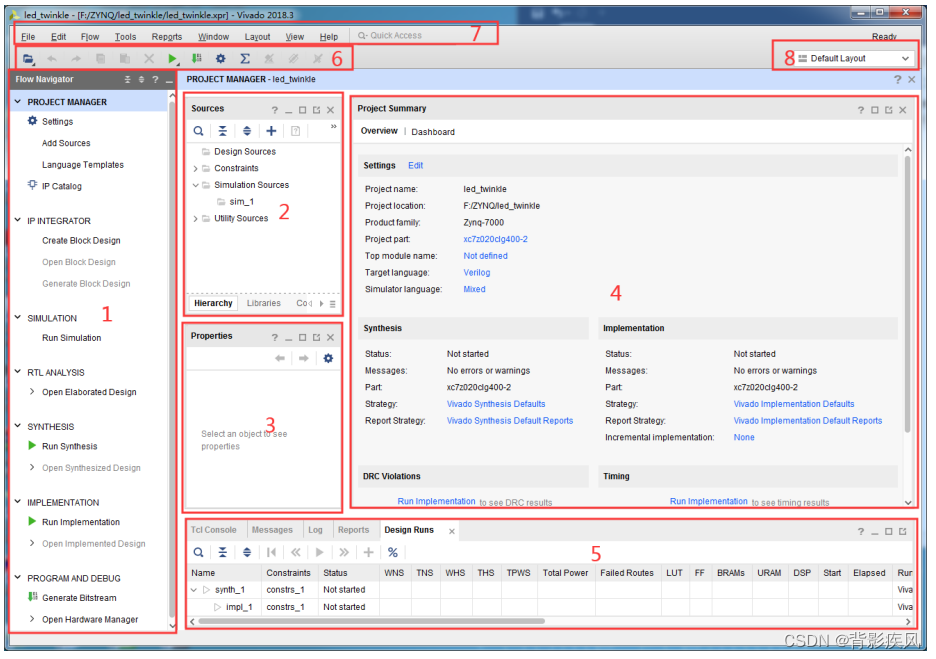

咱们打开Vivado工程之后展示在我们面前的应该是上图的界面,具体创建工程请参考网络教程。初学者可能会比较蒙圈,第一因为界面是英文,第二,因为对软件比较陌生。其实我们开始并不需要了解太多细节,但是我还是会根据序号框介绍,先给大家一个整体的印象。

- Flow Navigator,即流程导航器,这是今天学习的重点,里面包含了整个Vivado的设计流程。

- 数据窗口,这个窗口分为 Source 和 Netlist 两个栏目,Source栏目用来管理工程文件和展示我们设计的层次。

- Properties(特征)窗口,展示选择的文件的特征信息,即有关所选逻辑对象或器件资源的特性信息。

- WorkSpace窗口,这个窗口在每个设计流程中所展示的信息都不一样,下面摘录正点原子对WorkSpace窗口内容的总结:

- 运行状态与运行结果窗口,这部分是对各个流程状态和结果的展示。包括了:Tcl Console:允许您输入 Tcl 命令,并查看以前的命令和输出的历史记录。• Messages:显示当前设计的所有消息,按进程和严重性分类,包括“Error”、“Critical Warning”、 “Warning”等等 • Log:显示由综合、实现和仿真 run 创建的日志文件。 • Reports:提供对整个设计流程中的活动 run 所生成的报告的快速访问。 • Designs Runs:管理当前工程的 runs。

- 主工具栏,主工具栏提供了对 Vivado IDE 中最常用命令的单击访问。

- 主菜单栏,主菜单栏提供对 Vivado IDE 命令的访问。

- 窗口布局(Layout)选择器:Vivado IDE 提供预定义的窗口布局,以方便设计过程中的各种任务。 布局选择器使您能够轻松地更改窗口布局。或者,可以使用菜单栏中的“Layout”菜单来更改窗口布局。

上面是对Vivado IDE界面的一个大致的介绍,这并不是今天的重点;感觉复杂是正常的,使用时间长了之后自然而然就会熟悉了,这里建议大家没事就挨个点一遍(反正点一点又不要钱)

设计流程

Vivado IDE最突出的一个亮点就是左侧的Flow Navigator,这个窗口,从上到小包含了使用Vivado进行硬件设计的整个流程,我们有必要对设计流程进行细致的分析:

我们首先要理解Vivado的设计初衷:即提升生产力

这句话比较抽象,但是无外乎概括出来就是两点:

- 设计重用:核心就是IP核

- 快速开发:核心就是BlockDesign

上面的话总结来说就是Vivado IDE的开发核心就是以一个个子IP作为核心部件,并在BlockDesign中对这些部件进行调用,组合成一个系统,再对这个系统进行分析与综合。

IP核可以是用户自己的,也可以使用官方提供的。这样的好处就是避免重复造轮子。

所以从现在开始,我们要明确一个十分重要的思路:

开发流程:设计 --> 综合 --> 实现--> 生成比特流

设计

系统设计的过程主要在 IP INTERGRATOR 当中进行。

也可以通过添加源文件通过传统的方法进行:

综合

所谓的综合就是将RTL语言转换为基本的触发器,选择器,加法器乘法器等等数字电路的组合,这个过程主要在SYTHESIS中进行。

注意,一般我们在综合之前要先进行引脚约束和时序约束。

实现

实现就是IMPLEMENT,主要的作用就是将综合后的电路使用PL的资源进行生成,因此必须要先进行综合之后才能进行实现。

实现完成后,其实就可以生成实际的比特流了,因此实现也是最接近实际的一个操作,实现之后再进行仿真,我们就称为 “后仿真 ”,实现之前的仿真,我们叫“前仿真”

生成比特流

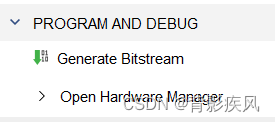

比特流就是FPGA进行编程的二进制文件,这个过程主要再在PROGRAM AND DEBUG中进行。

我们在这个窗口可以进行下载和在线的调试。

其它

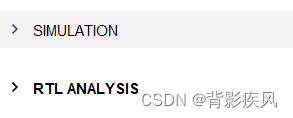

大家应该注意到了,其实Flow Navigator窗口还有另外两个栏目:

第一个是对RTL进行仿真,下面那个RTL ANALYSIS主要是对RTL进行一个分析,并且生成电路。同学们可能会疑惑,这个过程是否和综合重复了呢?

我的答案的否定的,为什么呢?因为世界上没有人能保证他们写的RTL代码一定正确。也许会出现语法错误,也许没有描述出自己想要的电路,如何不先经过一次检查,直接去综合,会消耗很多的时间(综合消耗的时间比较长)

因此,RTL ANALYSIS最大的作用就是综合前的检查。

结尾

上面的内容就是本讲的全部了,一口气说了这么多我也很无奈,因为百度能查到的资料十分有限,希望上面的内容能够解答初学者的疑惑,这也不枉我凌晨两点还在写这篇博客的初衷了。

本人能力有限,上述内容如有错误恳请各位留言斧正!