【AD9361 数字接口CMOS LVDSSPI】B 并行数据之CMOS

##接上一篇;

本节介绍 AD9361 数字接口CMOS &LVDS&SPI最后一张表中四种工作模式的具体配置及时序波形图。

目录

- 1、单端口半双工模式 (CMOS) *代称 SHC*

- 换句话说,最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。

- 这里提个问题,byte的范围是 -127~127 ? 还是 -128 ~127? 答案放在最后一篇吧

- 单端口TDD 时序(CMOS)

- 2、单端口全双工模式 (CMOS) *代称 SFC*

- 最大值是12‘b0111_1111_1111,即0x7FF;第一个字节是6‘b01_1111,即 0x1F,第二个字节是6'b11_1111 ,即0x3F。注意这里的“字节”不是8bit的标准字节。

- 最小值的数字量是12‘b0111_1111_1111,即 0x800;同理,第一个字节为 0x20,第二个字节为 0x00。

- 单端口TDD 时序(CMOS)

- 3、双端口半双工模式 (CMOS) *代称 DHC*

- 最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。

- 双端口TDD时序(CMOS)

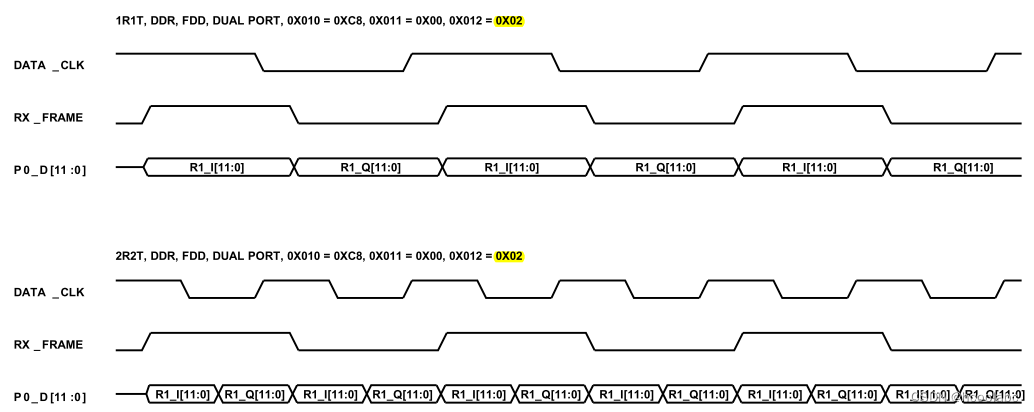

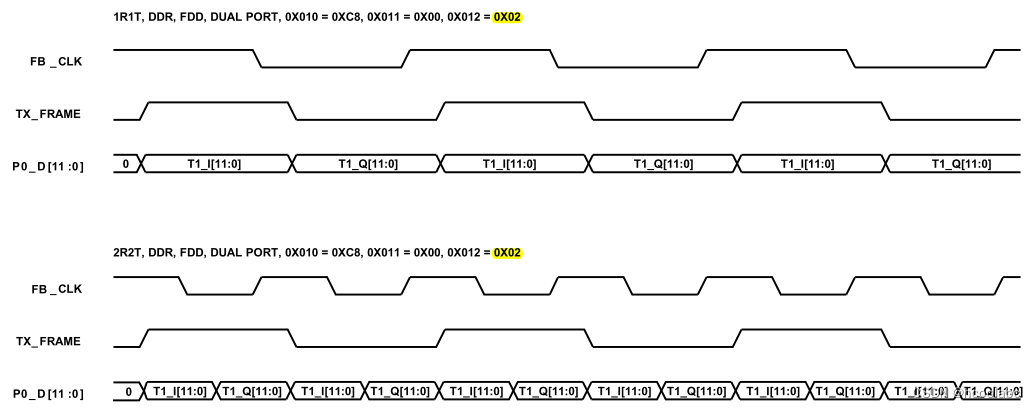

- 4、双端口全双工模式 (CMOS) *代称 DDC*

- 最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。

- 双端口FDD 时序(CMOS)

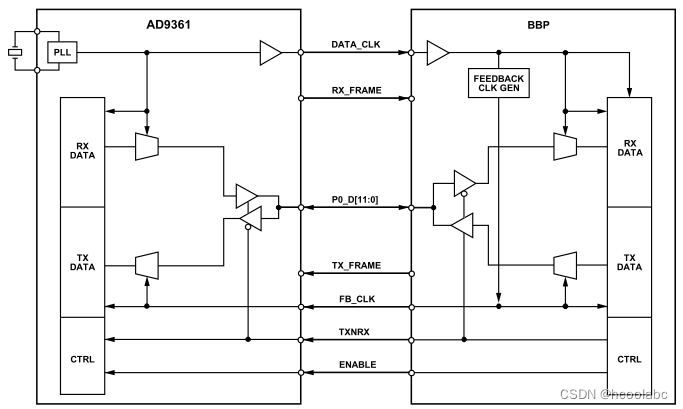

1、单端口半双工模式 (CMOS) 代称 SHC

【SINGLE PORT HALF DUPLEX MODE (CMOS)】

SHC模式用于需要TDD操作和数据速率低于61.44 MHz的应用。

在这种模式下,总线以双向方式使用,因此可以在同一条线路上接收或传输数据。此模式可用于所有接收器-发送器配置(1R1T、2R1T、1R2T 和 2R2T),通常用于 PCB 空间有限或 BBP 只有一个数据总线端口可用的情况。在此配置中,总线可以作为单数据速率 (SDR) 或双数据速率 (DDR) 运行。在此模式下,启用的端口在传输和接收操作之间多路复用,而未使用的端口被禁用。

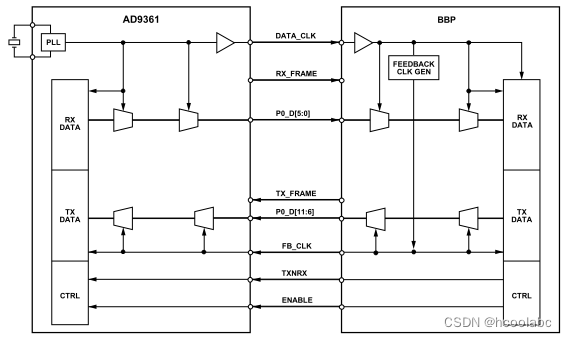

使能端口由 SPI 寄存器0x012中的交换端口位确定。下图显示了AD9361与BBP在这种工作模式下的连接。

在Rx突发期间,D[11:0]由AD9361驱动,因此DATA_CLK和D[11:0]之间的建立和保持时间允许BBP使用DATA_CLK捕获数据。

同样,在Tx突发期间,D[11:0]由BBP驱动,因此FB_CLK和D[11:0]之间的建立和保持时间允许AD9361使用FB_CLK捕获数据。

当ENABLE信号脉冲(或变为高电平)时,数据传输开始,数据传输结束被标记为ENABLE线路上的另一个脉冲(或当它返回低电平时)。

数据传输的方向由TXNRX信号决定。当该信号为低电平且ENSM处于Rx或FDD状态时,总线配置为接收方向(数据从AD9361传输到BBP)。当TXNRX被驱动为高电平且ENSM已脱离Rx或FDD状态时,ENSM将总线更改为发送方向(数据从BBP传输到AD9361)。

Rx_FRAME 和 Tx_FRAME 信号表示一组(帧)数据样本的开始。Rx_FRAME可以设置为在每次数据传输的突发开始时发生一次(仅一次高转换),或者在每帧开始时有一个上升沿,并以 50% 的占空比重复,直到数据传输完成。同样,Tx_FRAME接受 BBP 中的任一格式。

在传输突发期间,BBP 使用 FB_CLK 和 Tx_FRAME 驱动 P0_D[11:0] 上的数据值。在Rx突发期间,AD9361使用DATA_CLK和Rx_FRAME驱动P0_D[11:0]上的数据值。

采样数据以二进制补码格式进行,其中D[11]为数值最高有效位,D[0]为最低有效位。

换句话说,最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。

这里提个问题,byte的范围是 -127~127 ? 还是 -128 ~127? 答案放在最后一篇吧

在这种模式下,I 和 Q 数据样本在数据总线上时间交错。对于每个方向的单个射频路径(1R1T 系统),I 和 Q 样本以 2 路交错方式传输:

I, Q, I, Q, …

对于使用两个 Rx/Tx 通道的系统,来自 RF 通道 1 和 2 的 I 和 Q 样本以 4 路交错方式传输:

I1 , Q1 , I2 , Q2, I1 , Q1, I2, Q2, … …

当 配置为2R1T 或 1R2T 的系统,时钟频率、采样周期和数据捕获时序与为配置为2R2T 系统,所配置的时钟频率、采样周期和数据捕获时序相同。

但是,在仅使用单个通道的路径中,每个数据组中禁用通道的 I-Q 数据对未使用。AD9361忽略这些未使用的数据位。例如,在仅使用 Tx 通道 1 的 2R1T 系统中,发射突发将有两个未使用的时隙,如下所示:

I, Q, X, X, I, Q, X, X, …

BBP 可能会用任意数据值填充未使用的 X 数据位。这些值可以是固定的常数值,也可以重复前面的数据采样值以降低总线开关因数,减少反转功耗。

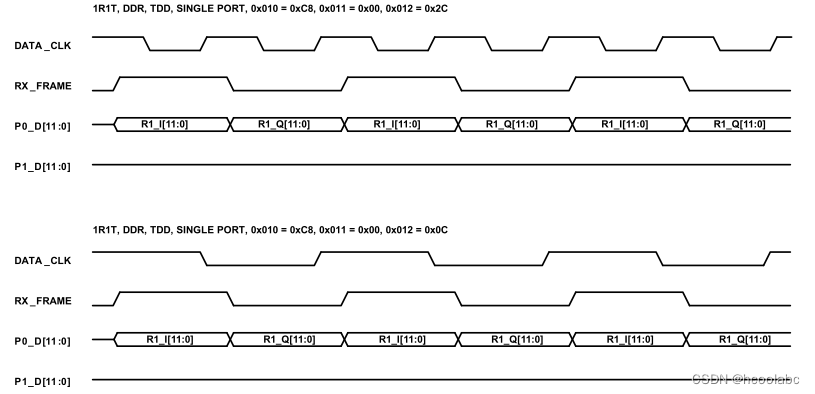

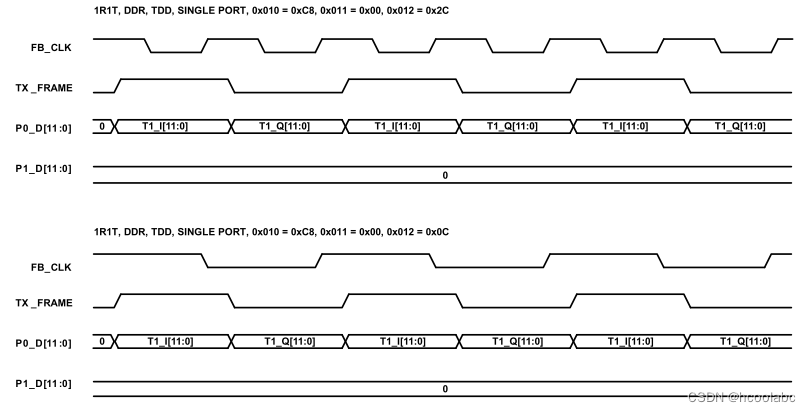

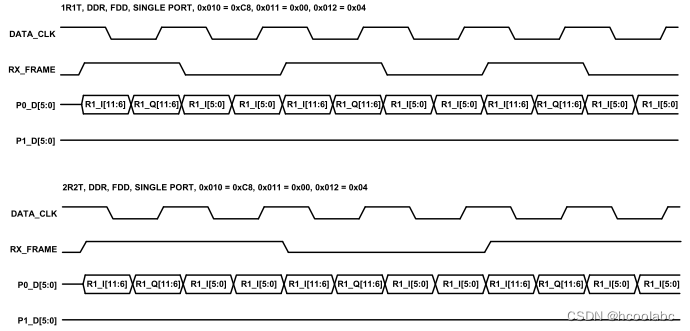

单端口TDD 时序(CMOS)

SINGLE PORT TDD FUNCTIONAL TIMING

本小节附图中的时序图说明了单端口TDD模式下总线信号之间的关系。这些图显示了 SDR 和 DDR 工作模式的时序示例。对于本节的所有后续部分,将仅显示 DDR 时序。本小节附图还包括 1R1T 场景的时序图,其中设置了 2R2T 时序位,强制数据传输格式与 2R2T 情况相同。此模式适用于可能需要在单通道和多通道操作之间切换但无法更改其数据传输格式的单端口系统。如果设备未配置 1R1T 模式,则 2R2T 位不起作用。

请注意,Tx_FRAME 和 Tx 数据的传输必须满足与 FB_CLK 相关的建立和保持要求。除了 1R1T 和 2R2T 场景外,还显示了 1R2T 和 2R1T 配置,以说明它们的时序与 2R2T 配置相同。在其他模式下,接收器和发射器通道的不同组合的行为也遵循 2R2T 时序行为,因此对于所有后续部分,图中省略了这些图。

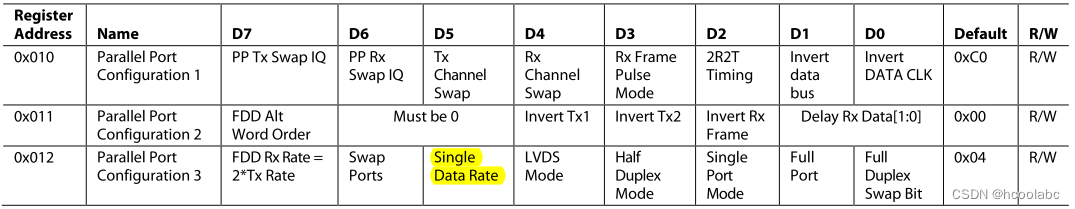

注意 :并行端口配置寄存器 0x010-0x012寄存器值

这1bit 设置为“0”时,使用DATA_CLK的双边沿;设置“1”时,使用DATA_CLK的单边沿。

这1bit 设置为“0”时,使用DATA_CLK的双边沿;设置“1”时,使用DATA_CLK的单边沿。

2、单端口全双工模式 (CMOS) 代称 SFC

SINGLE PORT FULL DUPLEX MODE (CMOS)

SFC模式用于需要FDD操作且数据速率低于30.72 MHz的应用。

在这种模式下,总线被分成两半,其中 6 位专用于 Rx 数据,6 位专用于 Tx 数据。此模式可用于所有接收机-发射机配置。在此配置中,总线可以作为 SDR 或 DDR 运行。在此示例中,仅启用 P0,并将数据总线拆分为单独的子总线。每个子总线同时工作,允许BBP和AD9361之间实现发送和接收数据的全双工。由于总线必须完成两倍于全双工模式的数据传输,因此数据总线必须以两倍于 TDD 模式的速度运行,以实现相同的发送和接收数据速率(因为每个总线在全双工模式下同时运行)。

上图显示了AD9361与BBP在SFC工作模式下的连接

发送数据由BBP驱动P0_D[11:6],因此FB_CLK和P0_D之间的建立和保持时间[11:6]允许AD9361使用FB_CLK来捕获数据。接收数据由AD9361在P0_D[5:0]上驱动,因此DATA_CLK和到达BBP的P0_D[5:0]之间的建立和保持时间使BBP能够使用DATA_CLK来捕获数据。ENABLE引脚上的一个脉冲(或上升沿)触发数据传输的开始,另一个脉冲(或下降沿)表示数据传输的结束。

Rx_FRAME 和 Tx_FRAME 信号表示一组(帧)数据样本的开始。Rx_FRAME信号可以设置为在每次数据传输的突发开始时出现一次(仅一次高电变),或者在每帧开始时有一个上升沿,并以 50% 的占空比重复,直到数据传输完成。同样,Tx_FRAME接受 BBP 中的任一格式。

发送数据样本以二进制补码格式传输,第一个 6 位字节 (P0_D[11:6]) 包含 MSB,第二个 6 位字节 (P0_D[11:6]) 包含 LSB。 P0_D[11] 是数值最高有效位,P0_D[6] 是最低有效位。

接收数据样本也以二进制补码格式传输,第一个 6 位字节 (P0_D[5:0]) 包含 MSB,第二个 6 位字节 (P0_D[5:0]) 包含 LSB。P0_D[5] 是数值最高有效位,P0_D[0] 是最低有效位。

在这两种情况下,就是原来12bit拆分2次6bit,发送或接受,之后再还原恢复;

最大值是12‘b0111_1111_1111,即0x7FF;第一个字节是6‘b01_1111,即 0x1F,第二个字节是6’b11_1111 ,即0x3F。注意这里的“字节”不是8bit的标准字节。

最小值的数字量是12‘b0111_1111_1111,即 0x800;同理,第一个字节为 0x20,第二个字节为 0x00。

在这种模式下,I 和 Q 数据样本在数据总线上时间交错。对于每个方向的单个射频路径(1R1T 系统),数据以 4 路交错方式传输,如下所示:

I MSB` , Q MSB , ILSB , Q LSB , …

对于具有两个有源 Rx/Tx 通道的系统,来自 RF 通道 1 和通道 2 的 I 和 Q 样本以 8 路交错方式传输,如下所示:

I1MSB , Q 1MSB , I 1LSB , Q 1LSB , I2MSB ,Q 2MSB ,I2LSB ,Q2LSB , …

对于具有 2R1T 或 1R2T 配置的系统,时钟频率、采样周期和数据捕获时序与为 2R2T 系统配置的时钟频率相同。但是,在仅使用单个通道的路径中,每个数据组中禁用通道的 I-Q 数据对未使用。AD9361忽略这些未使用的通道。例如,对于使用发射通道 1 的 2R1T 系统,突发发射将有四个未使用的时隙,如下所示:

I1MSB ,Q1MSB,I1LSB,Q1LSB,X,X,X,X, X , …

BBP 可以用任意数据值填充未使用的 X 通道。这些值可以是常量值,也可以重复上述数据采样值,以降低总线开关系数,从而降低功耗。

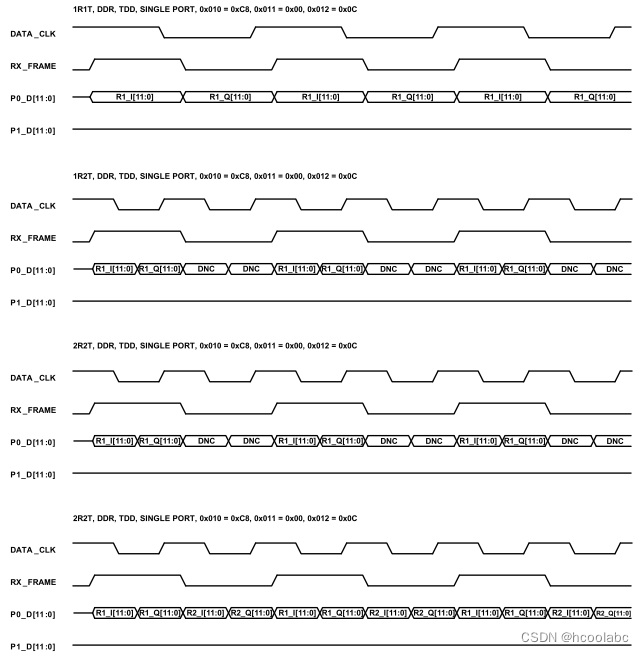

单端口TDD 时序(CMOS)

下面的时序图说明了单端口FDD模式下总线信号之间的关系。请注意,由于 2R1T 和 1R2T 系统遵循 2R2T 时序图,因此省略了它们。

3、双端口半双工模式 (CMOS) 代称 DHC

DUAL PORT HALF DUPLEX MODE (CMOS)

DHC模式用于需要TDD操作和高达122.88 MHz数据速率的应用。

在此模式下,使用两个数据端口,P0分配给I数据,P1分配给Q数据。端口在此模式下双向运行,数据方向由哪个通道处于活动状态决定:发送或接收。在此配置中,每条总线都可以作为 SDR 或 DDR 运行。此模式可用于所有接收机-发射机配置。

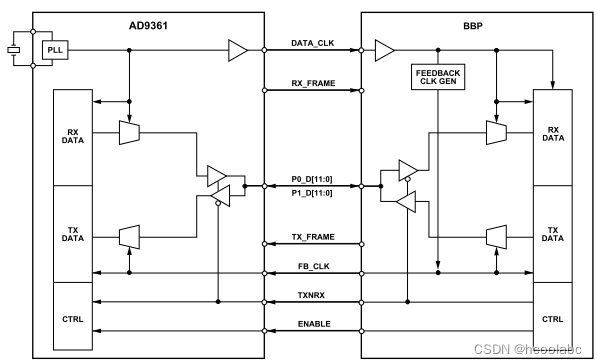

下图显示了AD9361与BBP在这种工作模式下的连接。

在Rx突发期间,两个端口均由AD9361驱动,因此DATA_CLK与到达BBP的每个数据样本之间的建立和保持时间使BBP能够使用DATA_CLK捕获数据。当ENABLE信号脉冲(或变为高电平)时,数据传输开始,数据传输结束被标记为ENABLE线路上的另一个脉冲(或当它返回低电平时)。

数据传输的方向由TXNRX信号决定。当该信号为低电平且AD9361处于FDD状态或Rx状态时,ENSM在接收方向上配置总线(数据从AD9361传输到BBP)。所有其他状态都会导致总线设置为高阻抗。当TXNRX被驱动为高电平时,ENSM将总线更改为发送方向(数据从BBP传输到AD9361)。在发射突发期间,两个端口(P0_D[11:0]和P1_D[11:0])均由BBP驱动,因此FB_CLK和每个D[11:0]之间的建立和保持时间允许AD9361使用FB_CLK捕获数据。

Rx_FRAME 和 Tx_FRAME 信号表示一组(帧)数据样本的开始。Rx_FRAME信号可以设置为在突发开始时出现一次(仅一次高电平转换),或者在每帧开始时有一个上升沿,并具有 50% 的占空比。同样,Tx_FRAME接受 BBP 中的任一格式。

数据样本以二进制补码格式进行,其中D[11]为数值最高有效位,D[0]为最低有效位。

最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。

对于每个方向上的单个射频路径(即 1R1T 系统),I 和 Q 样本分别用 P0_D[11:0] 上的 I 数据和 P1_D[11:0] 上的 Q 数据分开,如下所示:

P0: I, I, I, …

P1: Q, Q, Q, …

对于具有两个有源 Rx 通道的系统,RF 路径 1 和 RF 路径 2 的 I 和 Q 采样与 P0 上的 I 采样和 P1 上的 Q 采样以 2 路交错方式传输。

P0: I1 , I2 , I1, I2, …

P1: Q1, Q2, Q1, Q2, …

对于配置为 2R1T 或 1R2T 的系统,时钟频率、采样周期和数据捕获时序与配置为 2R2T 系统配置的时钟频率相同。

但是,在仅使用单个通道的路径中,每个数据组中禁用通道的 I-Q 数据对未使用。例如,对于仅使用 Tx 通道 1 的 2R1T 系统,Tx 突发将有两个未使用的通道,如下所示:

AD9361捕获

P0: I1, X, I1, X , …

P1: Q1,X,Q1,X , …

BBP 可以用任意数据值填充未使用的 X通道。这些值可以是常量值,也可以重复前面的数据采样值,以降低总线开关系数,从而降低功耗。

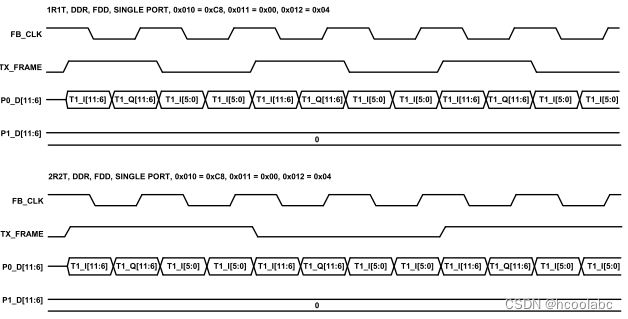

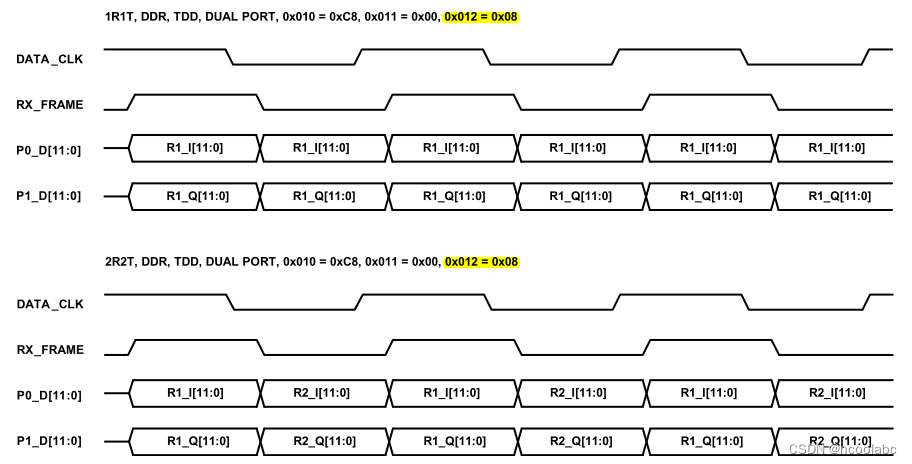

双端口TDD时序(CMOS)

DUAL PORT TDD FUNCTIONAL TIMING (CMOS)

下图的时序图说明了双端口TDD模式下总线信号之间的关系。请注意,由于 2R1T 和 1R2T 系统遵循 2R2T 时序图,因此省略了它们。

4、双端口全双工模式 (CMOS) 代称 DDC

DUAL PORT FULL DUPLEX MODE (CMOS)

DDC模式(全端口)用于需要FDD操作且数据速率低于61.44 MHz的应用。

在此模式下,使用两个数据端口,P0 用于接收数据,P1 用于传输数据。每条总线同时工作,允许在BBP和AD9361之间全双工传输Tx和Rx数据。对于此模式,每条数据总线必须以双端口TDD模式的两倍速度运行,才能实现相同的Tx和Rx数据速率(因为每个总线在全双工模式下同时运行)。在此配置中,每条总线都可以作为 SDR 或 DDR 运行。此模式可用于所有接收机-发射机配置。

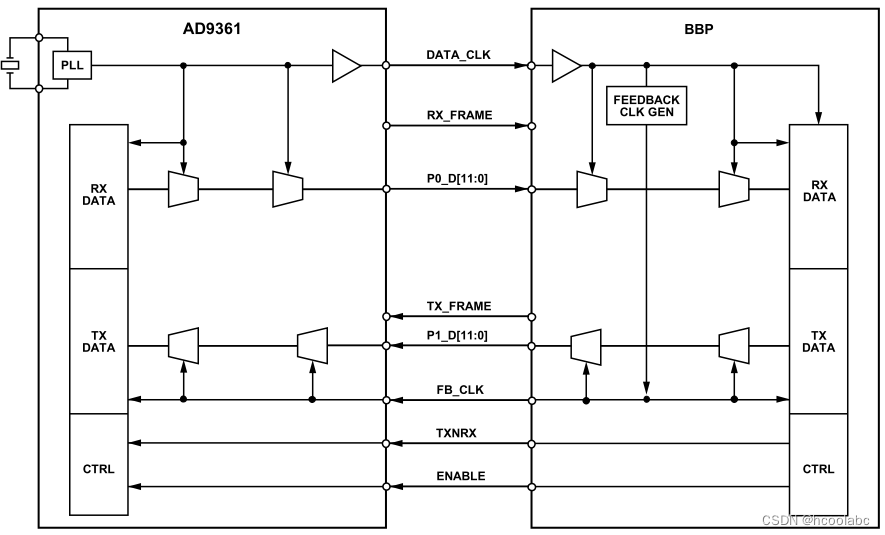

下图显示了AD9361与BBP在这种工作模式下的连接。

发送数据由BBP以P1_D[11:0]驱动,因此FB_CLK和数据之间的建立和保持时间允许AD9361使用FB_CLK来捕获数据。接收数据由AD9361以P0_D[11:0]驱动,因此DATA_CLK与到达BBP的数据之间的建立和保持时间使BBP能够使用DATA_CLK捕获数据。ENABLE引脚上的一个脉冲(或上升沿)触发数据传输的开始,另一个脉冲(或下降沿)表示数据传输的结束。

Rx_FRAME 和 Tx_FRAME 信号表示一组(帧)采样数据的开始。Rx_FRAME可以设置为在每次数据传输的突发开始时发生一次(仅一次高电平转换),也可以设置为在每帧开始时有一个上升沿,并以 50% 的占空比重复,直到数据传输完成。同样,Tx_FRAME接受 BBP 中的任一格式。

Tx 采样数据以二进制补码格式进行。P1_D[11]是数值最高有效位,P1_D[0]是最低有效位。Rx 采样数据也以二进制补码格式进行。P0_D[11]是数值最高有效位,P0_D[0]是最低有效位。

最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。

I和Q采样数据在每个方向上都在同一数据总线上传输。对于每个方向的单个射频路径,数据传输如下:

Px: I, Q, I, Q, I, Q, …

对于具有两个 Rx/Tx 通道的系统,来自 RF 通道 1 和 2 的 I 和 Q 样本携带如下:

Px: I1 , Q1, I2, Q2, …

对于具有 2R1T 或 1R2T 配置的系统,时钟频率、采样周期和数据捕获时序与为 2R2T 系统配置时相同。但是,在仅使用单个通道的路径中,每个数据组中禁用通道的 I-Q 数据对未使用。AD9361忽略这些未使用的通道。例如,对于使用 Tx 通道 1 的 2R1T 系统,Tx 突发将有两个未使用的通道,如下所示:

AD9361捕获

P1:I1、Q1、X、X…

BBP 可能会用任意数据值填充未使用的 X 通道。这些值可以是常量值,也可以重复前面的数据采样值,以降低总线开关系数,从而降低功耗。

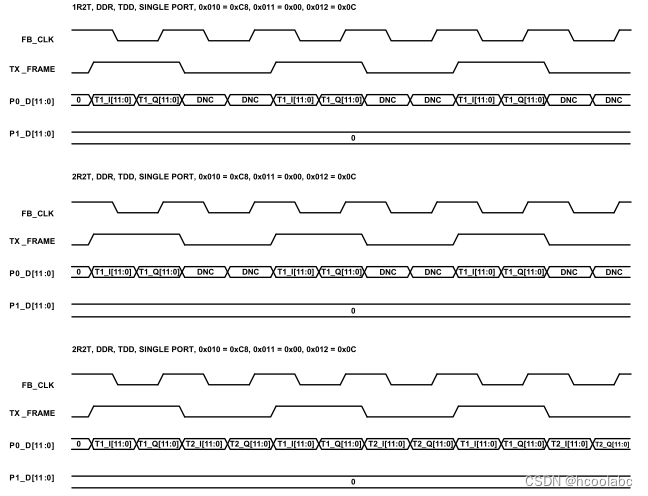

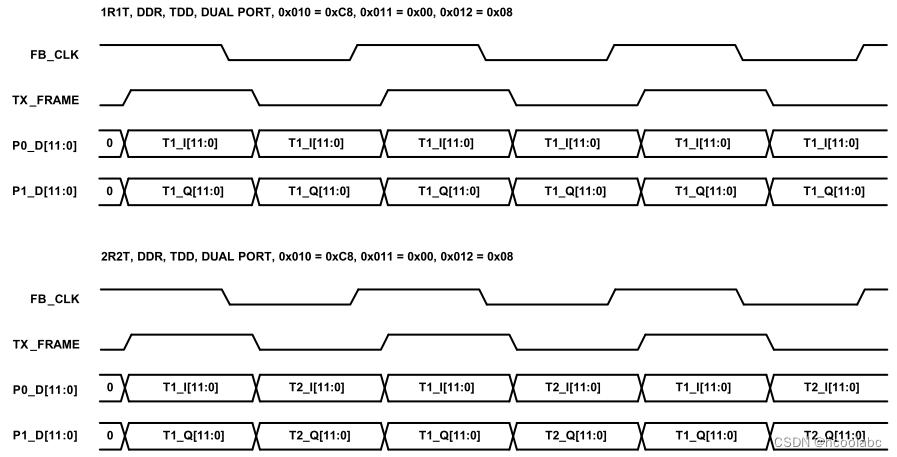

双端口FDD 时序(CMOS)

下图的时序图说明了双端口全双工模式下总线信号之间的关系。请注意,由于 2R1T 和 1R2T 系统遵循 2R2T 时序图,因此省略了它们。