ECO概念及理解

文章目录

- 何为ECO(What is ECO)

- ECO分类(ECO Category)

- ECO解释(ECO Illustration)

- 形式验证(Formality Check)

- ECO主要步骤(ECO Main Steps)

- 参考文献(Reference)

E C O ECO ECO中文翻译就是工程变更(Engineering Change Order)。很多工作几年的朋友,肯定或多或少都接触过这个事情。因为 d e s i g n design design中写的算法难免有 b u g bug bug,后仿用的case无法覆盖 100 % 100\% 100%的应用场景,以及实现过程中犯了某些错误等。

何为ECO(What is ECO)

E C O ECO ECO要干的事情:在后期修正你的 b u g bug bug,弥补你的罪。

讲到这里,我们需要简单介绍下 I C IC IC设计的 f l o w flow flow:

- 首先老大+牛人们在小黑屋开会,讨论大体架构,定下 s p e c spec spec,然后前端工程师吭哧吭哧写代码。写完代码开始搞验证仿真。等到大家仿真验证差不多的时候,几乎不再能抓到什么新 b u g bug bug了,就会进入 R T L f r e e z e RTL\ \ freeze RTL freeze阶段。

- R T L f r e e z e RTL\ \ freeze RTL freeze就是说,从今天起,大家谁也不能再修改 R T L RTL RTL了。这是一个分水岭。在 f r e e z e freeze freeze之前,你仿真也好,看代码也好, F P G A FPGA FPGA验证也好,发现的任何 b u g bug bug,都可以通过修改 R T L RTL RTL的方式进行直接更正。但是 f r e e z e freeze freeze之后,被 f r e e z e freeze freeze的 R T L RTL RTL将会进行综合, S T A STA STA,然后送给后端人员,做 f l o o r p l a n floor\ \ plan floor plan,电源综合,时钟综合,布局布线等等。这些后端流程都是极其耗时的,而且通常不可逆的,就是说,你让我再做一遍,结果就不能保证了。

那么问题来了,假如说,我在某一天发现了一个 b u g bug bug,我向老大提出要求修改 R T L RTL RTL,这个时候后端同事 f l o w flow flow已经完成了综合, f l o o r p l a n floor\ \ plan floor plan和布局,走到布线阶段了。你总不能说我把 R T L RTL RTL改了,然后重新综合一遍,让后端的同事再重新从 f l o o r p l a n floor\ \ plan floor plan做起?小心有刀飞过来。

假如运气不好,明天就 t a p e o u t tapeout tapeout了,难道你还要去改 R T L RTL RTL,哪有时间让你再做一遍后端的全flow?运气再差点,已经 t a p e o u t tapeout tapeout了,工艺厂刚刚启动生产线,做完了第一块掩模板的光刻,你跟他们说:停!我还有个 b u g bug bug!要从 R T L RTL RTL重新做?你当然不可能重新从 R T L RTL RTL做起,因为时间耽误不起。后端好不容易做收敛的成果也浪费不起。

幸运的是,上面的情况你都可以用 E C O ECO ECO搞定:

ECO分类(ECO Category)

从 f r e e z e freeze freeze到 t a p e o u t tapeout tapeout之间的 E C O ECO ECO叫 p r e M A S K E C O pre\ MASK\ ECO pre MASK ECO;

- Tapeout前的ECO:时间成本相对较小

很多公司(特别是大公司),他们一般都有规定哪个阶段必须 R T L f r e e z e RTL\ \ freeze RTL freeze,这个时候不会也不允许再更新新的 R T L RTL RTL,即使后面仿真验证有 b u g bug bug。为什么不让更新 R T L RTL RTL呢?因为此时数字后端工程师可能都做好布局布线, t i m i n g timing timing也没什么大问题了,都准备开始修 t i m i n g timing timing了。如果此时 r e l e a s e release release新的 R T L RTL RTL,那就意味着需要重新跑整个 f l o w flow flow,从综合到 P R ( p l a c e m e n t & r o u t e ) PR(placement \& route) PR(placement&route),再到 f i x i n g t i m i n g fixing\ \ timing fixing timing。一方面会严重影响整个项目的 T a p e o u t Tapeout Tapeout时间,从而影响 W a f e r o u t Wafer out Waferout和芯片上市的时间。另外一方面,数字后端工程师可能有想骂人的冲动。

因此,此时数字前端负责写 c o d i n g coding coding的工程师只能在 f i n a l R T L final RTL finalRTL的基础上,通过写 E C O ECO ECO脚本的方式来实现功能上的 E C O ECO ECO。

- Tapeout过程的ECO:时间成本较大

当数字后端实现后的 d e s i g n design design, t i m i n g timing timing已经符合 s i g n o f f signoff signoff(签发)标准, D R C DRC DRC已经 c l e a n clean clean, L V S LVS LVS 已经 p a s s pass pass, I R d r o p IR\ \ drop IR drop, M V R C MVRC MVRC, F o r m a l i t y Formality Formality, D R C P L U S DRCPLUS DRCPLUS等都已经 p a s s pass pass。但是数字前端设计工程师还没来得及做完大部分 c a s e case case的后仿,而且芯片又面临着 T i m i n g − T O − M a r k e t Timing-TO-Market Timing−TO−Market的压力。此时,老板可能会说先 T a p e o u t Tapeout Tapeout吧(就是开始传 G D S I I GDSII GDSII给 F o u n d a r y Foundary Foundary厂)。为什么敢这么做呢?是在赌博吗,呵呵。其实肯定有赌博的成分,但是更多的还是自信(认为不会出大问题)。因为,前一周左右 f o u n d a r y foundary foundary会先做 b a s e l a y e r base\ \ layer base layer的加工。只要后期仿真发现的问题,不需要再添加额外的 c e l l cell cell,就不耽误之前的 T a p e o u t Tapeout Tapeout(此处有点像流水线)。即使发现需要新加几个 c e l l cell cell,这个时候仍然可以通过替换后端实现过程中所加的 E C O c e l l ECO\ \ cell ECO cell或者 s p a r e c e l l spare\ \ cell spare cell来实现。(如何预先加 E C O c e l l ECO\ \ cell ECO cell 和 s p a r e c e l l spare\ \ cell spare cell,后续会专门讨论)

t a p e o u t tapeout tapeout之后,已经加工完芯片的晶体管,但是还没有做晶体管连线期间的 E C O ECO ECO叫做 p o s t M A S K E C O post\ MASK\ ECO post MASK ECO。

- Tapeout后的ECO:时间成本、资金成本较大

当芯片已经回来,在测试过程中发现的 b u g bug bug,然后又必须 f i x fix fix掉的 b u g bug bug(无法通过软件绕过去或者代价太高)。这个时候需要通过 E C O ECO ECO来解决。这个时候做 E C O ECO ECO的代价相对前面两种大很多,都是要消耗很多的真金白银,而且有芯片量产的巨大压力。改动少的可能就改几层 M e t a l l a y e r Metal\ \ layer Metal layer,多的可能就需要动十几层 M e t a l l a y e r Metal\ \ layer Metal layer,甚至重新流片。做 E C O ECO ECO之前,老板肯定会让数字前端设计工程师出 E C O ECO ECO方案,同时让后端工程师进行评估,主要评估需要改动的层数, t i m i n g timing timing是否能快速收敛等方面的风险。

ECO解释(ECO Illustration)

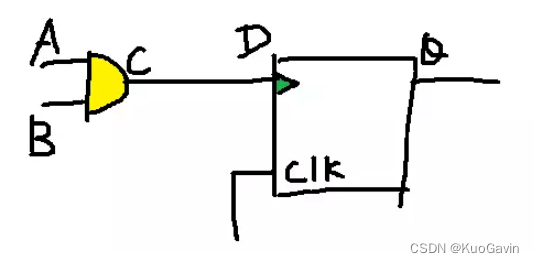

所谓 E C O ECO ECO,简单讲就是直接修改 n e t l i s t netlist netlist。简单的例子,下图是综合之后的一小部分的电路图:

写成 R T L RTL RTL就是: D = A & B D = A \& B D=A&B。假如说,我发现这段代码有 b u g bug bug,我需要改成: D = ( A & B ) ∣ E D = (A \& B) | E D=(A&B)∣E;

怎么办呢?你需要做的是在 n e t l i s t netlist netlist中加入一个或门,然后将上图中的 C C C端与 E E E端作为或门的输入。新的电路图如下:

怎么实现这种转变呢?后端工具有专门的 C M D CMD CMD支持,你可以采用这种 C M D CMD CMD写个脚本,大致内容如下。当然,这只是个示意,实际的 C M D CMD CMD形式不是这样的,但是思想是一样的。

addcell OR;

connect C to OR.A1 port;

connect E to OR.A2 port;

connect OR.Z port to D;

以上这种搞法仅仅适用于 p r e M A S K E C O pre\ MASK\ ECO pre MASK ECO,在这个 E C O ECO ECO阶段,你可以往设计里面添加各种 c e l l cell cell。这样既修复了 b u g bug bug,又不需要重新综合,避免了后端的各阶段成果被破坏掉。比如综合的电源网络,时钟树,以及布局规划都没有被破坏。如果你修改 R T L RTL RTL,那么必须重新做综合,然后再从 f l o o r p l a n floor plan floorplan开始…

到了 p o s t M A S K post\ MASK post MASK阶段, E C O ECO ECO就变得更加艰难些。因为这个时候,芯片已经 t a p e o u t tapeout tapeout,工艺厂( f o u n d r y foundry foundry)已经开始加工基底层了( b a s e base base层,也就是晶体管层),所以这个时候,没有办法再往设计里面添加 c e l l cell cell,比如与门,非门,寄存器等等。但是因为这个时候,芯片的互连线( w i r e wire wire层)还没有加工,所以,你可以改变晶体管的互连线。

但是你并不是没有 c e l l cell cell可以用,实际的芯片在 t a p e o u t tapeout tapeout时候,都会在 c h i p chip chip中撒很多多余的 c e l l ( r e d u n d a n t c e l l ) cell(redundant\ cell) cell(redundant cell),这些 c e l l cell cell分散在各处,用来给 p o s t M A S K E C O post\ MASK\ ECO post MASK ECO使的。像下图中,红色的点就是四散分布的多余的 c e l l cell cell,它们可以是 M U X MUX MUX,与非门,或非门, b u f f e r buffer buffer,寄存器等等:

同样是之前提到的那段 E C O ECO ECO,在 p o s t M A S K post\ MASK post MASK阶段,假如你能在这些多余的 c e l l cell cell里面找到一个或门,然后将 C C C和 E E E的连线改变一下,接到这个或门上,再把或门的输出接到寄存器的 D D D端,就可以解决这个 b u g bug bug。假如运气不好,找不到或门,或许你就得想别的方法,比如找到一个或非门和非门,然后串联起来做一个或门。

当然了,到了这个阶段,因为所有 c e l l cell cell的位置和类型都已经固定了,所以连线长短也无法改变, c e l l cell cell大小也不由你挑,很有可能你虽然修完了 b u g bug bug,但是用 S T A c h e c k STA\ check STA check会发现 t i m i n g timing timing无法满足。但是已经没辙了,只能死马当活马医了,乞求这条 p a t h path path是 f a l s e p a t h false\ path false path或者 m u l t i c y c l e multicycle multicycle吧。

形式验证(Formality Check)

修完 E C O ECO ECO,怎么确定有没有修正确呢?这就涉及到形式验证。

前端人员,写完 E C O C M D ECO\ CMD ECO CMD之后,利用 E C O ECO ECO命令修改旧 n e t l i s t netlist netlist,得到新的 n e t l i s t netlist netlist,然后将这个 n e t l i s t netlist netlist与修改过后的 R T L RTL RTL做对比,确定二者功能一样,就叫做形式验证。如下图:

形式验证有专门的 E D A EDA EDA工具来做,既可以用来比较两个 R T L RTL RTL功能是否一样,也可以比较 R T L RTL RTL的功能与综合之后的 n e t l i s t netlist netlist功能是否一样,还可以比较两个 n e t l i s t netlist netlist功能是否一样。这里我们不做深入讲解。

需要明白的是,前端工程师既要修改 n e t l i s t netlist netlist,也要修改 R T L RTL RTL,然后将两者进行对比,确定功能一致。这样才能保证 E C O ECO ECO命令完成了你想要的功能。

ECO主要步骤(ECO Main Steps)

总结下数字 I C IC IC设计中做 E C O ECO ECO的主要步骤(数字后端工程师必须熟练掌握以下几点工作,第一点除外):

- 数字前端工程师制定 E C O ECO ECO方案(验证方案有效性,可行性);

- 写 E C O ECO ECO脚本;

- 后端工程师根据 E C O ECO ECO脚本,进行摆放 c e l l cell cell和连线(手工或自动的方式);

- 形式验证(确保后端进行变更后的功能和前端 E C O ECO ECO方案功能一致性);

- 确认基于 T a p e o u t Tapeout Tapeout版本的 G D S I I GDSII GDSII所有改动的层(通过 c a l i b r e calibre calibre跑 L a y o u t V e r s u s L a y o u t Layout\ \ Versus\ \ Layout Layout Versus Layout);

- 重新做 d u m m y i n s e r t i o n dummy\ \ insertion dummy insertion或者人工改 d u m m y dummy dummy;

- 再次进行 t i m i n g s i g n o f f timing\ \ signoff timing signoff( F i x i n g a l l s e t u p , h o l d , t i m i n g d r c , e t c Fixing\ \ all\ \ setup,\ \ hold,\ \ timing\ \ drc,\ \ etc Fixing all setup, hold, timing drc, etc);

- 再次跑 D R C ( 设计规则检查 ) & L V S DRC(设计规则检查)\&LVS DRC(设计规则检查)&LVS并 f i x v i o l a t i o n s fix\ \ violations fix violations;

- R e l e a s e Release Release新的 G D S I I GDSII GDSII

参考文献(Reference)

- IC科普文:ECO的那些事

- 数字IC设计中ECO的那些事,其实并不是事