基于Xlinx的时序分析与约束(5)----衍生时钟约束

衍生时钟约束语法

衍生时钟(Generated Clocks,又称为生成时钟)是指由设计中已有的主时钟通过倍频、分频或者相移等操作后产生的新的时钟信号,如由MMCM或PLL或由组合逻辑生成的倍、分频时钟信号。

衍生时钟约束必须指定时钟源,在对衍生时钟进行约束时,并不指直接对其周期、相位等进行描述,而是描述其与源时钟的关系,如倍频因子、分频因子、相位关系等。衍生时钟与源时钟之间的关系可以是:

- 简单的频率分频

- 简单的频率倍频

- 频率倍频与分频的组合,获得一个非整数的比例,通常由MMCM或PLL完成

- 相移或波形反相

- 占空比改变

- 上述所有关系的组合

衍生时钟约束的一般语法是:

create_generated_clock -name <generated_clock_name>\

-source <master_clock_source_pin_or_port>\

-multiply_by <mult_factor>\

-divide_by <div_factor>

<pin_or_port>

- \是换行符号

- -name后的generated_clock_name是用于指定的衍生时钟名

- -source后的 master_clock_source_pin_or_port 是源时钟的物理节点,源时钟可以是一个主时钟、虚拟时钟或者衍生时钟

- -multiply_by后是衍生时钟相对于源时钟的倍频系数,值必须大于等于1.0

- -divide_by后是衍生时钟相对于源时钟的分频系数,值必须大于等于1.0

- <pin_or_port>是衍生时钟的物理节点

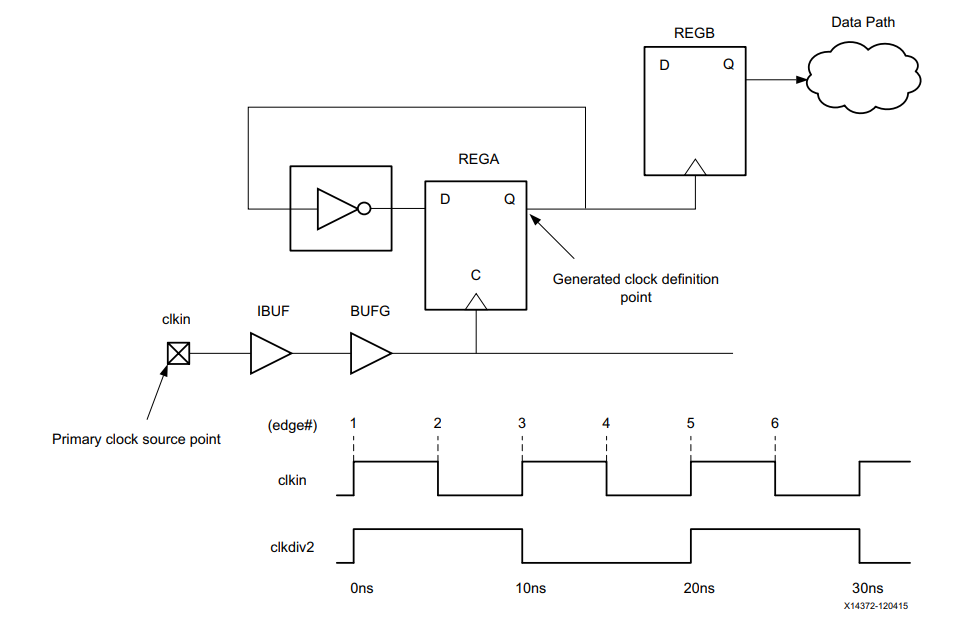

例1:2分频的衍生时钟约束

下图中,主时钟clkin的时钟周期为10ns,通过组合逻辑的形式构建了2分频的衍生时钟clkdiv2,

根据源时钟的不同认定方式,clkdiv2的衍生时钟约束有两种表达方式:

(1)源时钟是主时钟clkin

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 \ [get_pins REGA/Q]

(2)源时钟是REGA的时钟管脚

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -divide_by 2 \ [get_pins REGA/Q]

例2:-edges选项描述的2分频衍生时钟

除了用选项-divide_by来描述外,也可以使用-edges选项来描述上面的2分频衍生时钟。其表示方法如下:

# waveform specified with -edges instead of -divide_by

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -edges {1 3 5} \ [get_pins REGA/Q]

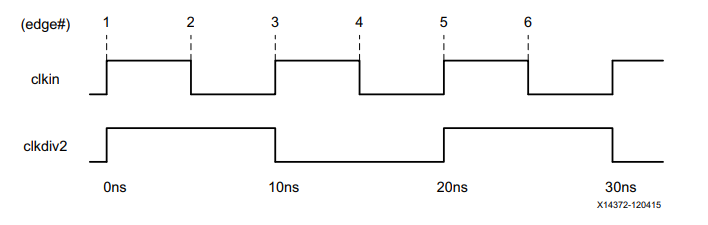

其中的 -edges {1 3 5} 分别表示衍生时钟的第一个上升沿是源时钟的第1个边沿;衍生时钟的第一个下降沿沿是源时钟的第3个边沿;衍生时钟的第2个上升沿是源时钟的第5个边沿。通过这种边沿之间的对应关系间接描述了源时钟与衍生时钟之间的倍、分频关系。

例3:-edges选项与-edge_shift描述的衍生时钟(占空比改变)

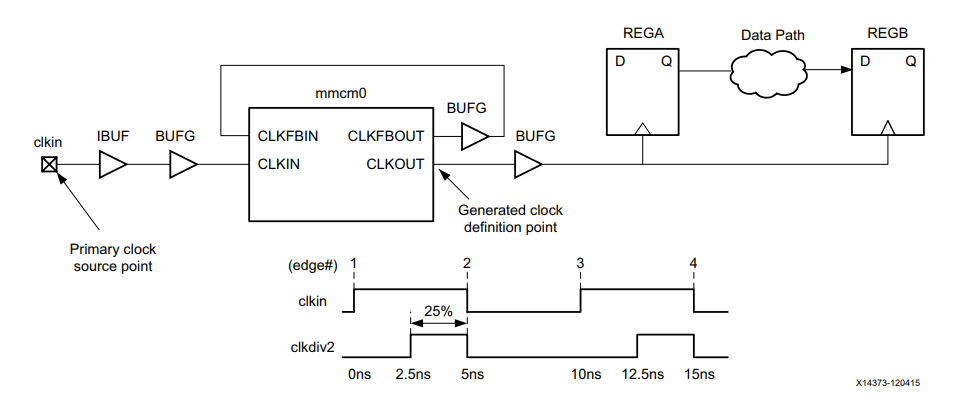

下图是一个用MMCM实现的衍生时钟,源时钟周期10ns,占空比50%。衍生时钟占空比25%,周期10ns,相移90度。

这个衍生时钟可以被约束为:

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkshift -source [get_pins mmcm0/CLKIN] -edges {1 2 3} \

-edge_shift {2.5 0 2.5} [get_pins mmcm0/CLKOUT]

-edges {1 2 3}和 -edge_shift {2.5 0 2.5}共同表示:

- 衍生时钟的第一个上升沿在源时钟的第1个边沿并加上2.5ns的相移,即其在0+2.5=2.5ns处

- 衍生时钟的第一个下降沿在源时钟的第2个边沿并加上0ns的相移,即其在5+0=5ns处

- 衍生时钟的第二个上升沿在源时钟的第3个边沿并加上2.5ns的相移,即其在10+2.5=2.5ns处

例4:同时使用-divide_by 和 -multiply_by

假设例4的其他情况均为例3相同,不同的是衍生时钟是源时钟的4/3倍,所以可以描述为:

create_generated_clock -name clk43 -source [get_pins mmcm0/CLKIN] -multiply_by 4 \ -divide_by 3 [get_pins mmcm0/CLKOUT]

非常经典的使用倍频系数和分频系数来描述的衍生时钟。

衍生时钟约束实战

在了解了衍生时钟时钟约束的语法后,我们接着来学习一下,如何具体地在vivado中使用它。

我们首先新建一个简单的工程,并实现以下代码:

module test(

input sys_clk, //50M

input rst,

output out

);

assign out = clk_div2;

reg clk_div2;

wire pll_clk;

//2分频

always @(posedge pll_clk)begin

if(rst)

clk_div2 <= 0;

else

clk_div2 <= ~clk_div2;

end

//PLL实现125M

clk_wiz_0 pll_inst

(

// Clock out ports

.clk_out1 (pll_clk), // output clk_out1

.reset (rst), // input reset

.locked (), // output locked

.clk_in1 (sys_clk) // input clk_in1

);

endmodule代码主要实现的功能:

- 输入时钟50M的sys_clk,经PLL后倍频到100M的pll_clk

- 100M的pll_clk使用组合逻辑2分频到50M的clk_div2

(1)Vivado自动推导的衍生时钟

使用PLL或者MMCM生成的衍生时钟,是可以不用做衍生时钟约束的,vivado会自动推断出衍生时钟的相位、频率等参数。

自动推导的好处在于当MMCM/PLL/BUFR的配置改变而影响到输出时钟的频率和相位时,用户无需改写约束,Vivado仍然可以自动推导出正确的频率/相位信息。劣势在于,用户并不清楚自动推导出的衍生时钟的名字,当设计层次改变时,衍生时钟的名字也可能改变。但由于该衍生时钟的约束并非我们自定义的,因此可能会没有关注到它名字的改变,当我们使用这些衍生时钟进行别的约束时,就会出现错误。

解决办法就是用户自己手动写出自动推导的衍生时钟的名字,也仅仅写出名字即可,其余的不写。如下如所示:

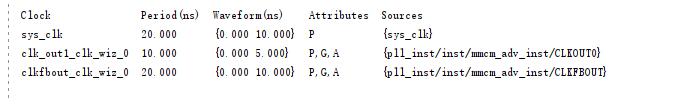

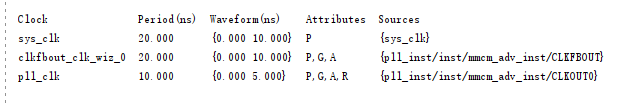

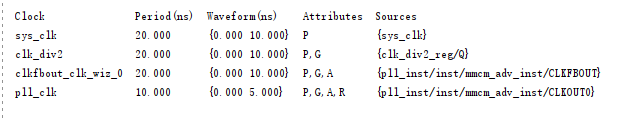

比如上面的代码,使用了PLL生成一个2倍频的时钟,且我们没有做衍生时钟约束,在Tcl界面输入:report_clocks,会发现自动推到出了3个时钟,一个是主时钟sys_clk,一个是PLL生成的时钟clk_out1_clk_wiz_0,最后一个是PLL自动生成的反馈时钟clkfbout_clk_wiz_0(和我们使用PLL的方式有关,这里不管它)

接着我们新建一个xdc文件,命名为timing.xdc,用来存储各种XDC指令。

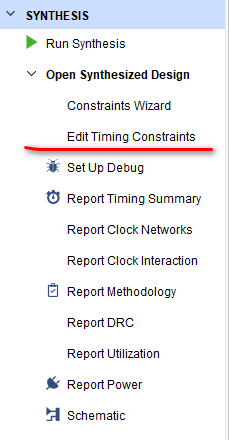

接着可以使用GUI界面来创建时序约束语句。在创建了XDC文件后,把工程综合完成,点击 edit timing constraints,打开时序约束编辑界面:

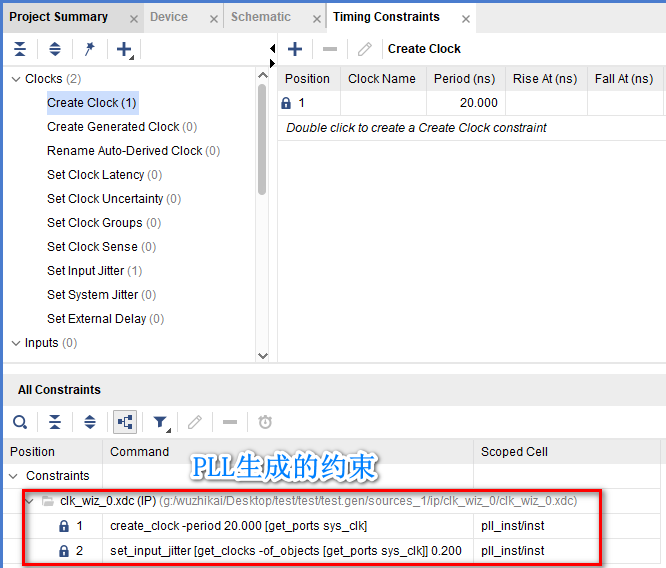

此时已经由PLL生成了两条约束:一条是主时钟约束,另一条是jitter约束。

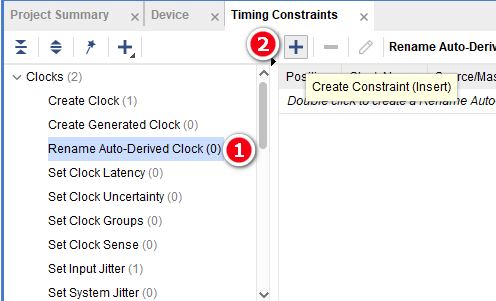

PLL生成的2倍频时钟clk_out1_clk_wiz_0 的名字是自动生成的,看上去很奇怪,我们可以自己把它改成特定的有意义的名字:

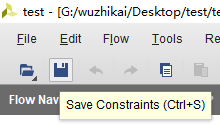

此时vivado左侧的保存约束按钮又可以按下了,按下将这一条语句保存:

此时再在Tcl界面输入:report_clocks,会发现名字已经改了:

(2)手动推导的衍生时钟

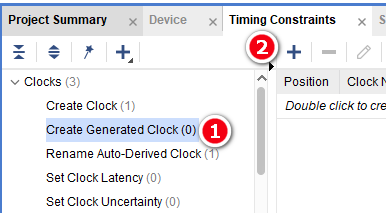

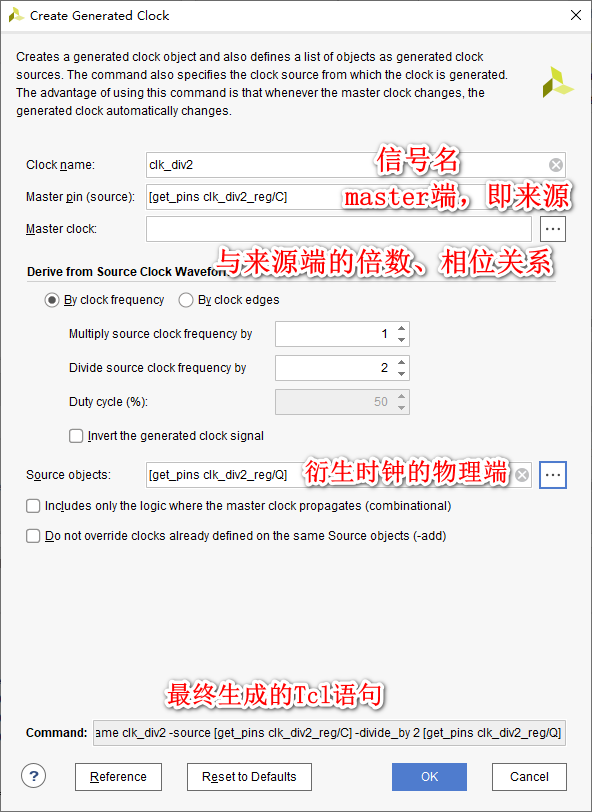

除了PLL和MMCM自动推出的衍生时钟外,我们自己用组合逻辑构建的分频时钟等,均需要自己手动写约束,约束的语法在上面已经介绍过了,这里说下用GUI界面来生成。

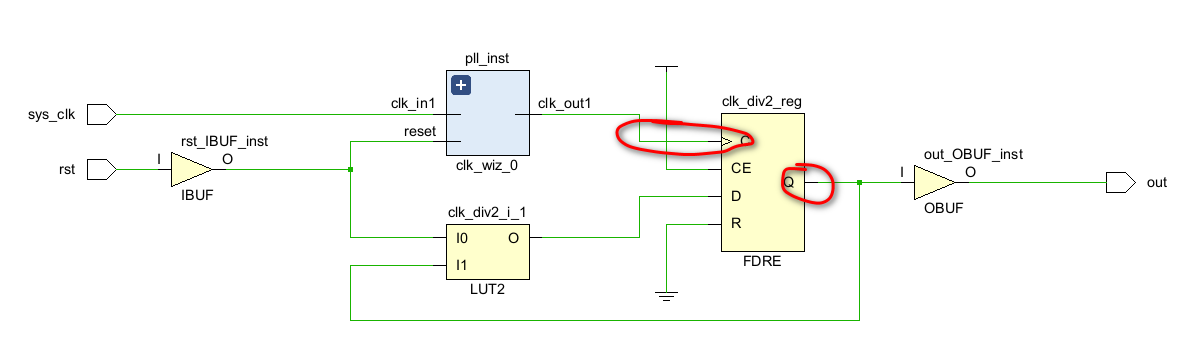

我们首先打开综合界面下的原理图:

可以看到2分频衍生时钟的master端是clk_div2_reg的C端,而source端则是 clk_div2_reg的Q端。

接着按如下步骤操作:

此时vivado左侧的保存约束按钮又可以按下了,按下将这一条语句保存:

此时再在Tcl界面输入:report_clocks,会发现多出来了一个手动推导的衍生时钟clk_div2:

- 📣博客主页:wuzhikai.blog.csdn.net

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵

- 📣您有任何问题,都可以在评论区和我交流📞!

- 📣创作不易,您的支持是我持续更新的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!