CXL-GPU: 全球首款实现百ns以内的低延迟CXL解决方案

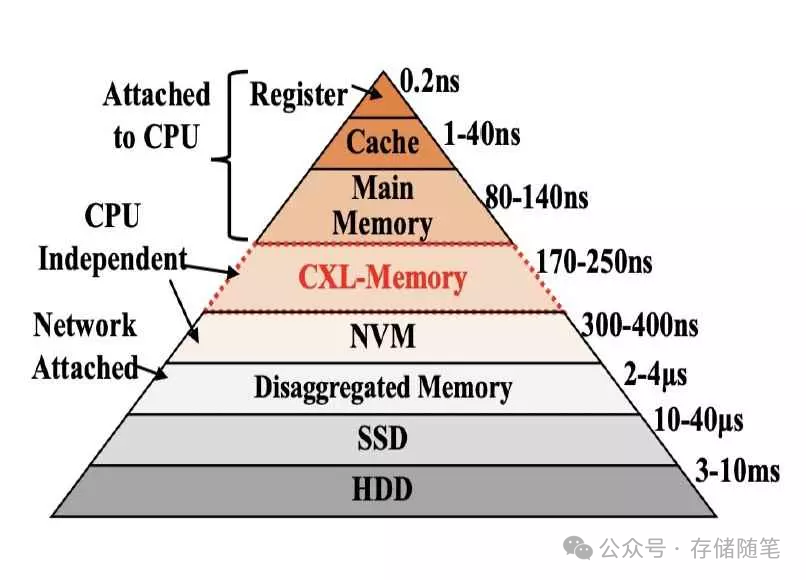

数据中心在追求更高性能和更低总拥有成本(TCO)的过程中面临三大主要内存挑战。首先,当前服务器内存层次结构存在局限性。直接连接的DRAM与固态硬盘(SSD)存储之间存在三个数量级的延迟差异。当处理器直接连接的内存容量耗尽时,就必须转向SSD,导致处理器处于等待状态。这种等待,即延迟,对计算性能产生重大负面影响。

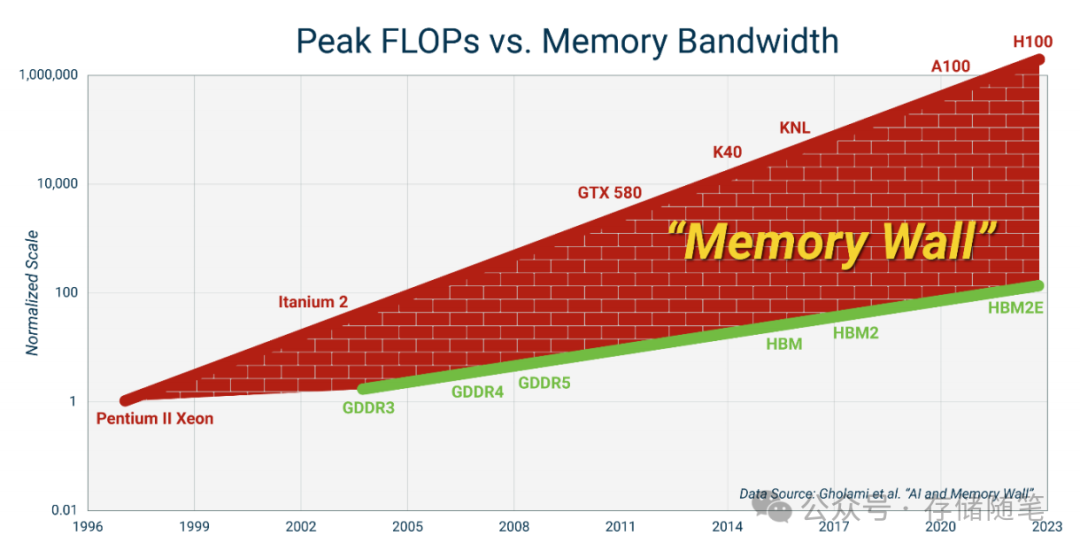

其次,多核处理器的核心数增长速度远远超过主内存通道的数量。这意味着超过一定数量的处理器核心会因缺乏足够的内存带宽而无法充分发挥效能,从而削弱了额外核心带来的优势,也就是出现了内存墙的问题。

高端GPU设计中,比如英伟达发布的HGXH200 GPU搭载了141GB的HBM3e内存,用于提升性能和处理大型数据集的能力,已经在一定程度上缓解了内存容量不足的问题。但,随着加速计算的普及,即加速器配备有自己的直接连接内存,未充分利用或被闲置的内存资源问题日益凸显。

在过去的尝试中,面对内存墙的问题,主要遇到以下四个挑战:

-

有限的内存带宽和容量可扩展性:传统内存系统在增加带宽和容量方面面临局限。随着数据密集型应用需求的增长,对内存资源的消耗急剧上升,但内存技术的发展却难以匹配这种快速增长的需求。这导致在处理大规模数据集时,系统因内存不足或数据交换速率慢而受到限制。

-

与本地内存显著的延迟差距:当引入外部或扩展内存解决方案时,它们通常具有比直接连接在CPU上的本地内存更高的访问延迟。这种延迟差影响了应用程序的响应时间和整体性能,特别是在那些对延迟敏感的应用场景下,如实时交易处理或高性能计算。

-

专有的系统配置和部署:早期尝试通过定制或专有解决方案来克服内存墙,这些方案往往需要特定的硬件和软件配置,导致部署复杂且不灵活。这种专属性意味着升级或维护成本高,且不能轻松地跨不同平台复用。

-

与流行应用软件的复杂集成:为了利用新的内存技术,软件需要进行相应的修改或优化,以便能够有效利用扩展的内存资源。然而,这种集成工作不仅技术上复杂,还可能需要大量的开发资源和时间,特别是当涉及到已经广泛使用的流行应用程序时,它们的代码库庞大且改动影响广泛。

以往尝试突破内存墙的努力受限于技术、成本和兼容性等多方面的难题,这些挑战阻碍了内存系统的高效扩展和应用性能的全面提升。

为了解决这些问题,业界正积极寻求新的技术和标准,比如Compute Express Link (CXL),它旨在通过提供标准化的高速互连来提高内存带宽、降低延迟,并简化内存扩展的软件集成,从而有效地打破内存墙的限制。

扩展阅读:

-

CXL:拯救NVMe SSD缓存不足设计难题

-

如何利用CXL技术突破内存墙?

-

CXL与PCIe世界的尽头|你相信光吗?

-

浅析CXL P2P DMA加速数据传输的原理

-

下一代分层存储方案:CXL SSD

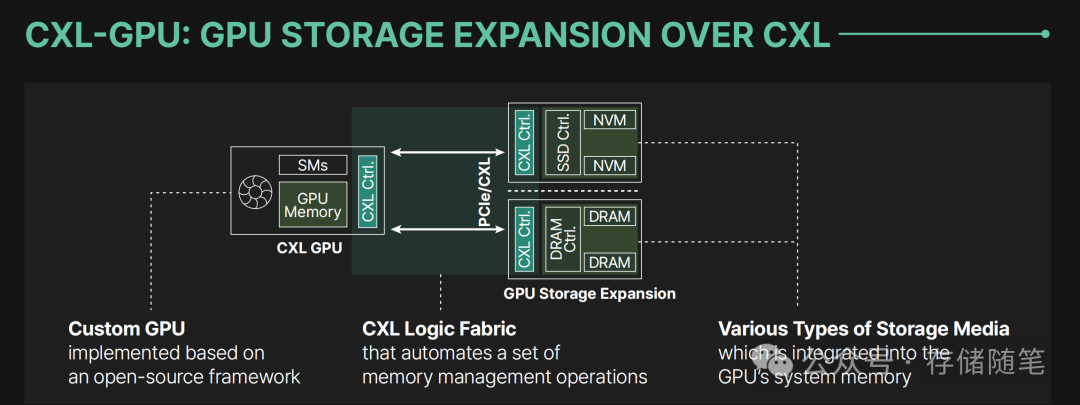

为了克服GPU内存容量限制,同时尽量减少性能损失,韩国一家公司Panmnesia提出了一项基于CXL技术的GPU存储扩展方案。

Panmnesia是一家在内存扩展和计算加速技术方面走在前列的创新型企业,其解决方案对于推动AI、云计算和高性能计算等领域的发展具有重要意义。通过不断技术创新和优化,Panmnesia正努力将CXL技术推向新的高度,为全球的系统开发商和制造商提供高性能、低成本的内存扩展解决方案。

-

端点(Endpoints, EPs):在CXL架构中,EPs可以是各种类型的存储设备,包括基于非易失性存储器(NVM)的固态硬盘(SSDs)和DRAM。这些设备通过CXL接口直接与计算单元通讯,降低了访问延迟,提升了数据传输速率。

-

计算单元访问:CXL允许GPU或其他计算单元如同访问本地内存一样,直接通过标准的加载/存储指令来读写这些外挂的存储设备,从而避免了通过CPU和系统内存作为中介的传统做法,减少了数据搬运的开销和延迟。

-

异步通信机制:CXL的异步通信特性为数据密集型应用提供了重要优势,特别是在深度学习、大规模数据分析等场景下,能够更加高效地管理数据流,减少等待时间,提升整体计算效率。

-

内存空间映射:CXL通过PCIe物理层,将EPs映射到主机的内存空间中,使得这些存储资源对计算单元来说就像是扩展的系统内存,简化了编程模型,便于软件层面的利用和管理。

Panmnesia公司突破性地开发出了全球首款实现两位数纳秒级往返延迟的CXL控制器,这一创新直接回应了GPU存储扩展领域的一项重大挑战。当前,GPU内部缺乏原生支持CXL逻辑结构和子系统的机制,无法直接将DRAM或SSD作为端点(EPs)来扩展内存。为此,Panmnesia填补了市场空白,设计了一系列至关重要的硬件层级,这些层级全面支持CXL的所有关键子协议,并将它们整合进了一个统一的控制器之中。

Panmnesia的创新之处

Panmnesia研发的CXL控制器,凭借其独特的低延迟CXL IP,解决了内存扩展中的一大难题——延迟。公司成功开发并完成了CXL控制器IP的硅片制造过程,确保所有CXL通信操作均能在极低的延迟下执行。这一控制器展现出了两位数纳秒级的往返延迟,这是迄今为止报道中最快的。

通过优化物理层、链接层和事务层的操作,Panmnesia的CXL控制器能够应用于包括CPU、交换机、加速器和内存扩展器在内的多种系统设备,自动化加速内存管理操作。这样,用户可以在保证性能损失最小化的同时,实现理想的内存扩展方案,降低TCO。

Panmnesia CXL IP控制器技术亮点

-

先进制程技术:展示了控制器的硅片布局,采用了台积电(TSMC)的先进技术进行制造。这意味着控制器不仅在技术上处于前沿,还具备高性能和低功耗的特性。

-

全面协议兼容:该CXL控制器设计符合CXL 3.1标准,同时向下兼容CXL 2.0和1.1版本,保证了其在不同平台上的广泛适用性。

-

低延迟性能:经过严格测试,控制器实现了两位数纳秒级别的往返延迟,这一成绩包括了标准内存操作与CXL数据包(flit)传输间的协议转换时间。这样的低延迟对于高性能计算和实时数据处理至关重要。

-

硬件集成验证:控制器不仅在硬件RTL上被成功集成到内存扩展器中,还在GPU和CPU的原型设计中进行了验证,展现了其在多样化计算硬件环境下的高效能与高兼容性。

性能对比分析

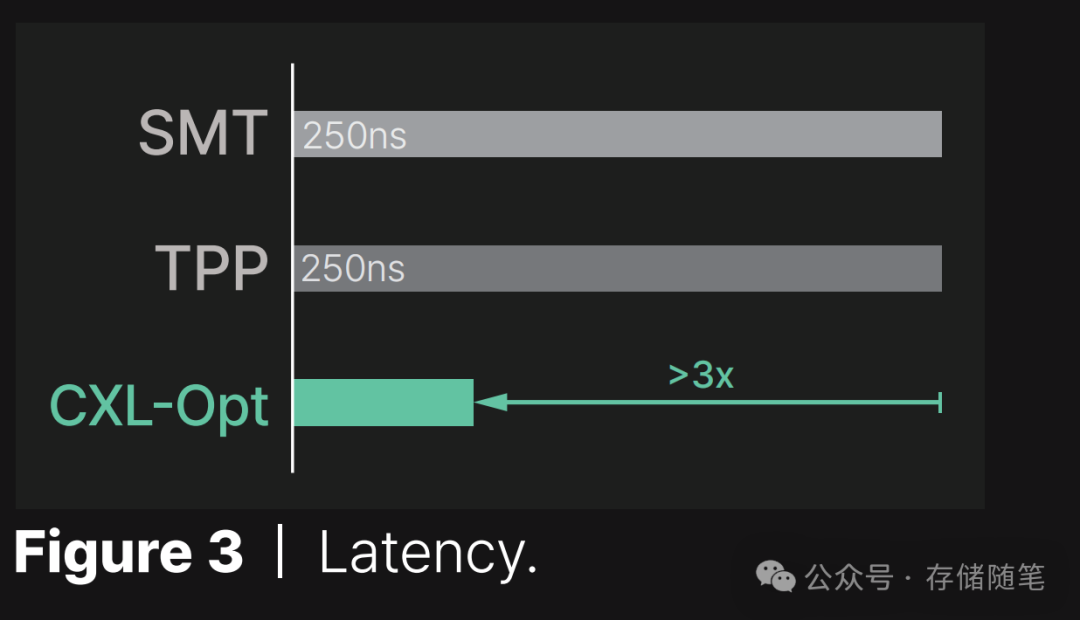

为了更好地说明其技术优势,Panmnesia将自家CXL控制器(CXL-Opt)的往返延迟与市场上其他两款解决方案SMT5和TPP6进行了比较。结果显示,CXL-Opt控制器的延迟至少比SMT和TPP快3倍(具体数字还未公开)。尽管关于SMT和TPP的具体硅片信息并未公开,但据推测它们可能是基于PCIe架构。相比之下,Panmnesia的CXL控制器从物理层到链路层,再到事务层,都针对CXL进行了全方位的优化,这解释了其显著的性能优势。

在设计和集成GPU架构以开发用于存储扩展的EP设备时,Panmnesia采取了一种创新策略,将CXL控制器的功能与内存/SSD控制器的功能相结合。这一结合使得CXL控制器能够将其后端存储空间扩展到主机系统中,这部分被定义为主机管理的设备内存(HDM)。然而,与GPU架构的集成面临着独特的挑战,因为EP需要被GPU的缓存系统识别。与常规EP直接对接的方式不同,这种情况需要更精细的设计。

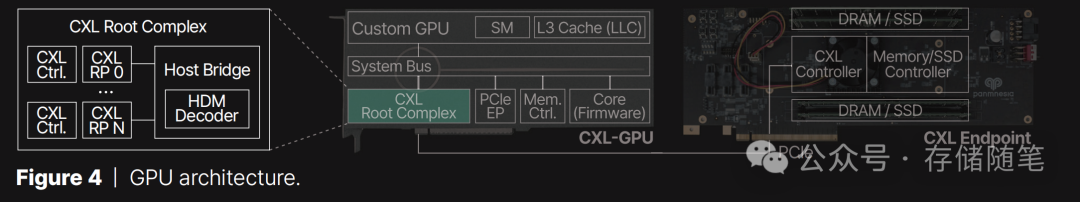

为了解决这些挑战,Panmnesia设计了一个特殊的CXL RC,它配备了一个带有多个RP的主机桥接器。下图左侧展示了这一配置,其中主机桥接器一侧连接到系统总线端口,另一侧则连接多个CXL根端口。这一设置的关键组件之一是一个HDM解码器,负责管理每个根端口的系统内存地址范围,即主机物理地址(HPA)。这些根端口设计灵活,可以通过PCIe连接支持DRAM或SSD EP。

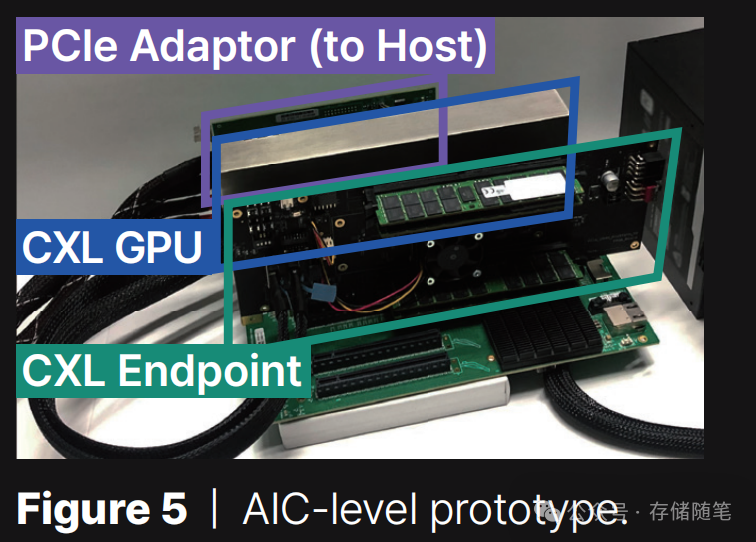

将CXL RC嵌入到Panmnesia基于开源框架定制的GPU架构中,该定制GPU专门设计以优化CXL功能的集成,确保与CXL控制器和EP设备的无缝协作。为了实现这一高度集成的系统,包括定制GPU和EP设备,Panmnesia利用了基于7纳米FPGA的定制AIC卡,如下图所示。这一FPGA平台不仅提供了快速原型设计和验证的途径,还允许高度的硬件灵活性和可编程性,从而适应未来可能的升级和优化。

Panmnesia的GPU架构设计和集成方案通过创新地融合CXL控制器与内存/SSD控制器功能,创建了一个高度优化的系统,该系统不仅解决了与GPU缓存系统兼容的问题,还通过一个灵活且高效的CXL RC设计,实现了对不同类型EP设备的支持。这一方案利用先进的FPGA技术实现,展示了面向未来的大规模深度学习和高性能计算应用的内存扩展解决方案。

Panmnesia在解决大型数据处理挑战方面,对比了三种不同的GPU系统配置,以评估它们在提高存储容量和效率方面的效果。这三种配置分别是:

-

UVM(Unified Virtual Memory): UVM技术通过在CPU和GPU间共享统一虚拟地址空间,允许两者通过共享指针访问数据。尽管此方法简化了内存管理,但在处理GPU页面错误时,必须依靠主机运行时软件进行干预,这导致了较高的延迟和性能开销。UVM以页面而非缓存行粒度迁移数据,经常导致数据传输量超出GPU实际需求。

-

CXL-Proto: 通过采用三星和Meta报告中提及的CXL端点原型,将CXL技术应用于GPU存储扩展,实现了250纳秒的延迟。虽然相比UVM有所改进,但仍有优化空间。

-

CXL-Opt: 同样基于CXL技术进行GPU存储扩展,但采用了Panmnesia自主研发的CXL控制器,该控制器实现了两位数纳秒级的往返延迟,并引入了额外的优化措施以减少读写延迟。这是目前性能最佳的解决方案。

性能评估

-

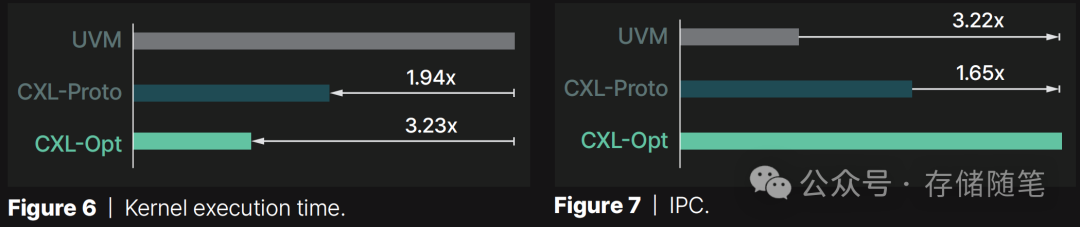

执行时间:通过比较三种配置在不同GPU内核上的执行时间,并以UVM为基准进行归一化,结果显示UVM的性能在所有测试中表现最差,这主要归因于处理GPU页面错误时主机运行时的干预开销。CXL-Proto通过允许GPU直接通过加载/存储指令访问扩展存储,避免了上述问题,使得执行时间比UVM缩短1.94倍。而CXL-Opt进一步优化,使用了低延迟的CXL控制器,执行时间比UVM缩短3.23倍。

-

每周期指令数(IPC):IPC值是衡量处理器效率的重要指标,表示每个时钟周期内完成的指令数量。在这个指标上,CXL-Opt相对于UVM和CXL-Proto分别展现出3.22倍和1.65倍的性能提升,进一步证明了其在提升GPU计算效率方面的显著效果。

这一创新的CXL控制器不仅解决了GPU内存扩展的迫切需求,也为AI、高性能计算及大数据处理等内存密集型应用提供了强大的支持。通过实现超低延迟的内存访问,Panmnesia的解决方案有望大幅提升系统的整体性能和效率,降低数据传输瓶颈,进而推动相关行业技术的进一步发展。此外,其全面的兼容性和高度优化的设计,为未来CXL技术在更广泛领域的应用奠定了坚实的基础。

另外,Panmnesia的CXL-GPU技术将在即将7月份于美国加州圣克拉拉举办的USENIX会议和ACM HotStorage活动中展示,具体细节预计会有更多的展示,小编持续关注中!

参考文献:https://panmnesia.com/#solution

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

-

万字长文|下一代系统内存数据加速接口SDXI解读

-

数据中心:AI范式下的内存挑战与机遇

-

WDC西部数据闪存业务救赎之路,会成功吗?

-

属于PCIe 7.0的那道光来了~

-

深度剖析:AI存储架构的挑战与解决方案

-

浅析英伟达GPU NCCL P2P与共享内存

-

3D NAND原厂:哪家芯片存储效率更高?

-

大厂阿里、字节、腾讯都在关注这个事情!

-

磁带存储:“不老的传说”依然在继续

-

浅析3D NAND多层架构的可靠性问题

-

SSD LDPC软错误探测方案解读

-

关于SSD LDPC纠错能力的基础探究

-

存储系统如何规避数据静默错误?

-

PCIe P2P DMA全景解读

-

深度解读NVMe计算存储协议

-

浅析不同NAND架构的差异与影响

-

SSD基础架构与NAND IO并发问题探讨

-

字节跳动ZNS SSD应用案例解析

-

CXL崛起:2024启航,2025年开启新时代

-

NVMe SSD:ZNS与FDP对决,你选谁?

-

浅析PCI配置空间

-

浅析PCIe系统性能

-

存储随笔《NVMe专题》大合集及PDF版正式发布!